- ОП. 03. ОСНОВЫ ЭЛЕКТРОНИКИ И ЦИФРОВОЙ СХЕМОТЕХНИКИ

- Самостоятельное изучение схемотехники. Основные понятия. Часть 1

- Проектирование логических схем с помощью функций алгебры логики

- Методические указания к выполнению ЛПЗ по Основам электроники и цифровой схемотехники

- Где P В – мощность переданного сигнала, PA – мощность принятого сигнала, а U В и UA — напряжения в точках A и B . Значение затухания, определенного поданной формуле всегда положительное, поскольку P В P А . Затухание 6дБ соответствует падению амплитуды сигнала вдове, 20дБ – в 10 раз. Кабели могут характеризоваться и погонным затуханием дБ/м. Чем меньше затухание — тем лучше кабель. С повышением частоты затухание увеличивается. К аномалиям импеданса приводят нарушения геометрии проводников (резкие изгибы, передавливания) и изоляции, применение отрезков кабеля с разными значениями импеданса. На концах отрезка источниками отражения сигнала могут и разъемы, если их импеданс не соответствует импедансу кабеля. Соединяемые кабелем устройства должны иметь соответствующий импеданс – при этом вся энергия передатчика будет уходить в линию, а приемник получит всю энергию, дошедшую до него по линии.

- Мерой степени согласованности импеданса является ослабление отраженного сигнала, или возвратные потери RL . Как и затухание этот параметр измеряется в децибелах.

- ACR = NEXT – Att

- План решения

- Обозначить простые высказывания, входящие в условие задачи, буквами (А, В, С,…).

- Используя логические связи между простыми высказываниями, составить сложные высказывания (условия задачи).

- Перемножить сложные высказывания, приравняв произведение к 1.

- Построить таблицу истинности.

- Записать ответ (выбрать из таблицы истинности при каких значениях простых высказываний логическая функция принимает значение истина).

- Задача 1

- Задача 2

- Цель работы:

- Задание 1. Исследование работы RS -триггера в статическом режиме.

ОП. 03. ОСНОВЫ ЭЛЕКТРОНИКИ И ЦИФРОВОЙ СХЕМОТЕХНИКИ

ИНИСТЕРСТВО ОБРАЗОВАНИЯ и молодежной политики КАМЧАТСКОГО КРАЯ

Краевое государственное профессиональное

образовательное бюджетное учреждение

ОП. 03. Основы электроники и цифровой схемотехники

09.01.03 Мастер по обработке цифровой информации

Профиль обучения: технический

Программа учебной дисциплины разработана на основе Федерального государственного образовательного стандарта (далее – ФГОС) и базисного учебного плана по профессии (профессиям) среднего профессионального образования (далее — СПО) 09.01.03 Мастер по обработке цифровой информации.

Краевое государственное профессиональное образовательное бюджетное учреждение «Паланский колледж»

Составитель программы учебной дисциплины

Преподаватель первой категории___________ И.В.Сальков

Паспорт программы учебной дисциплины

Структура и содержание учебной дисциплины

Условия реализации программы учебной дисциплины

Контроль и оценка результатов освоения учебной дисциплины

1. паспорт ПРОГРАММЫ УЧЕБНОЙ ДИСЦИПЛИНЫ

ОП.03.Основы электроники и цифровой схемотехники

1.1. Область применения программы

Программа учебной дисциплины является частью программы подготовки квалифицированных рабочих, служащих в соответствии с ФГОС по профессии

(профессиям) СПО 09.01.03 Мастер по обработке цифровой информации, входящей в укрупненную группу направлений подготовки 090000 Информатика и вычислительная техника по направлению подготовки 090100 Информатика и вычислительная техника. Профессия по ОК 016-94: оператор электронно-вычислительных и вычислительных машин.

Программа учебной дисциплины может быть использована в дополнительном профессиональном образовании (в программах повышения квалификации и переподготовки) на базе среднего (полного) общего образования и на базе основного общего образования, и профессиональной подготовке рабочих по профессии: оператор электронно-вычислительных и вычислительных машин.

1.2. Место дисциплины в структуре основной профессиональной образовательной программы: дисциплина входит в общепрофессиональный цикл.

2.3. Цели и задачи дисциплины – требования к результатам освоения дисциплины:

В результате освоения дисциплины обучающийся должен уметь:

определять параметры полупроводниковых приборов и элементов системотехники.

В результате освоения дисциплины обучающийся должен знать:

основные сведения об электровакуумных и полупроводниковых приборах, выпрямителях, колебательных системах, антеннах; усилителях, генераторах электрических сигналов;

общие сведения о распространении радиоволн;

принцип распространения сигналов в линиях связи;

сведения о волоконно-оптических линиях;

цифровые способы передачи информации;

общие сведения об элементной базе схемотехники (резисторы, конденсаторы, диоды, транзисторы, микросхемы, элементы оптоэлектроники);

логические элементы и логическое проектирование в базисах микросхем;

функциональные узлы (дешифраторы, шифраторы, мультиплексоры, демультиплексоры, цифровые компараторы, сумматоры, триггеры, регистры, счетчики);

запоминающие устройства на основе БИС/СБИС;

цифро-аналоговые и аналого-цифровые преобразователи.

1.4. Рекомендуемое количество часов на освоение программы дисциплины:

максимальной учебной нагрузки обучающегося — 80 часов, в том числе:

обязательной аудиторной учебной нагрузки обучающегося — 60 часов;

самостоятельной работы обучающегося — 20 часов.

2. СТРУКТУРА И СОДЕРЖАНИЕ УЧЕБНОЙ ДИСЦИПЛИНЫ

2.1. Объем учебной дисциплины и виды учебной работы

Самостоятельная работа обучающегося (всего)

Итоговая аттестация в форме в форме дифференцированного зачета

2.2. Тематический план и содержание учебной дисциплины ОП.03.Основы электроники и цифровой схемотехники

Содержание учебного материала, лабораторные работы и практические занятия, самостоятельная работа обучающихся

Раздел1. Полупроводниковые приборы.

Тема1.1. Основные сведения о полупроводниковых приборах.

Содержание учебного материала

Понятие «электровакуумный» и «полупроводниковый» прибор, их параметры.

Понятие «выпрямитель» и «колебательная система», их параметры.

Понятия «антенна», «усилитель», «генератор электрических сигналов», их параметры.

Общие сведения о распространении радиоволн.

Принцип распространения сигналов в линиях связи. Сведения о волоконно-оптических линиях.

Цифровые способы передачи информации.

Лабораторная работа. Освоение приемов работы с электроизмерительными приборами (амперметр, вольтметр, омметр).

Самостоятельная работа обучающихся

Систематическая проработка конспектов занятий, учебной и специальной технической литературы (по вопросам к параграфам, главам учебных пособий, составленных преподавателем).

Подготовка к лабораторным работам с использованием методических рекомендаций преподавателя.

Оформление лабораторных работ, отчетов и подготовка к их защите.

Работа с базами данных, библиотечным фондом (учебной литературой, официальными, справочно-библиографическими и периодическими изданиями), информационными ресурсами сети Интернет.

Самостоятельное изучение правил выполнения чертежей и технологической документации по ЕСКД и ЕСТП.

Источник

Самостоятельное изучение схемотехники. Основные понятия. Часть 1

Изучение цифровой схемотехники нужно начинать с теории автоматов. В этой статье можно найти некоторые элементарные вещи, которые помогут не потеряться в дальнейших статьях. Я постарался сделать статью легкочитабельной и уверен, что неподготовленный читатель сможет в ней легко разобраться.

Сигнал — материальный носитель информации, используемый для передачи сообщений по системе связи. Сигнал, в отличие от сообщения, может генерироваться, но его приём не обязателен (сообщение должно быть принято принимающей стороной, иначе оно не является сообщением, а всего лишь сигналом).

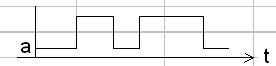

В статье рассматривается цифровой дискретный сигнал. Это такой сигнал, который имеет несколько уровней. Очевидно, что двоичный сигнал имеет два уровня — и их принимают за 0 и 1. Когда высокий уровень обозначается единицей, а низкий нулем — такая логика называется позитивной, иначе негативной.

Цифровой сигнал можно представить в виде временной диаграммы.

В природе дискретных сигналов не существует, по этому их заменяют аналоговыми. Аналоговый сигнал не может перейти из 0 в 1 мгновенно, по этому такой сигнал обладает фронтом и срезом.

Если рисовать упрощенно то это выглядит так:

1 — низкий уровень сигнала, 2 — высокий уровень сигнала, 3 — нарастание сигнала (фронт), 4 — спад сигнала (срез)

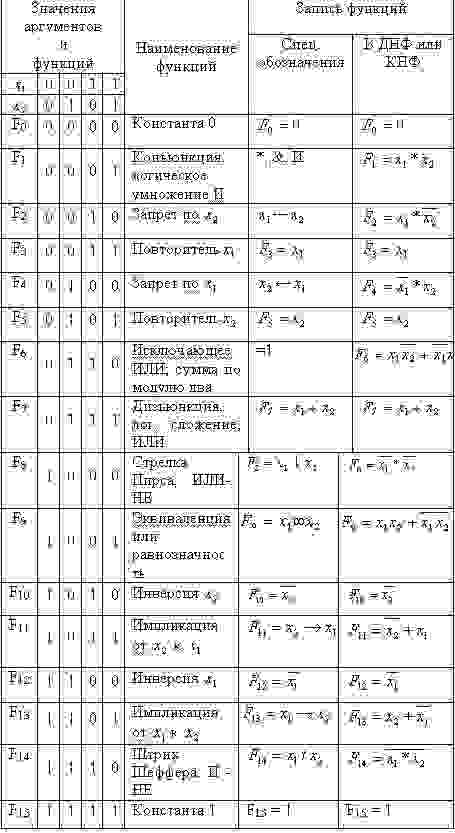

Сигналы можно преобразовывать. Для этого на практике используются логические элементы, а чтобы это записать формально используются логические функции. Вот основные:

Отрицание — инвертирует сигнал.

На схемах обозначается так:

Логическое ИЛИ (логическое сложение, дизъюнкция)

На схеме:

Логическое И (логическое умножение, конъюнкция)

На схеме:

Последние два могут иметь отрицание на выходе (И-НЕ, ИЛИ-НЕ). Значения их логических функций инвертируются, а на схеме выход рисуется кружочком.

Сводная таблица логических функций двух аргументов выглядит так:

Работа с логическими функциями основывается на законах алгебры логики, основы которых изложены в прикрепленном файле. Так же там есть задания для самоконтроля и контрольные вопросы по теме.

Проектирование логических схем с помощью функций алгебры логики

Логической схемой называется совокупность логических электронных элементов, соединенных между собой таким образом, чтобы выполнялся заданный закон функционирования схемы, иначе говоря, — выполнялась заданная логическая функция.

По зависимости выходного сигнала от входного все электронные логические схемы можно условно разбить на:

Схемы первого рода, т.е. комбинационные схемы, выходной сигнал которых зависит только от состояния входных сигналов в каждый момент времени;

Схемы второго рода или накапливающие схемы (схемы последовательностные), содержащие накапливающие схемы (элементы с памятью), выходной сигнал которых зависит как от входных сигналов, так и от состояния схемы в предыдущие моменты времени.

По количеству входов и выходов схемы бывают: с одним входом и одним выходом, с несколькими входами и одним выходом, с одним входом и несколькими выходами, с несколькими входами и выходами.

По способу осуществления синхронизации схемы бывают с внешней синхронизацией (синхронные автоматы), с внутренней синхронизацией (асинхронные автоматы являются их частным случаем).

Практически любой компьютер состоит из комбинации схем первого и второго рода разной сложности. Таким образом, основой любого цифрового автомата, обрабатывающего цифровую информацию, являются электронные элементы двух типов: логические или комбинационные и запоминающие. Логические элементы выполняют простейшие логические операции над цифровой информацией, а запоминающие служат для ее хранения. Как известно, логическая операция состоит в преобразовании по определенным правилам входной цифровой информации в выходную.

Можно считать, что элементарные логические функции являются логическими операторами упомянутых электронных элементов, т.е. схем. Каждая такая схема обозначается определенным графическим символом. (Они были представлены выше — Элементы И, ИЛИ, НЕ, ИЛИ-НЕ, И-НЕ)

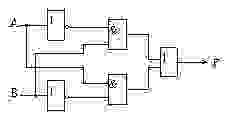

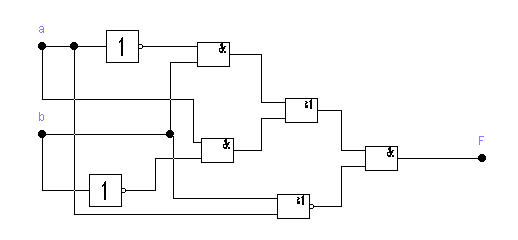

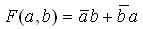

В качестве примера ниже представлена схема электрическая функциональная логического преобразователя (комбинационного автомата), реализующего логическую функцию

Для закрепления предлагаю, самостоятельно синтезировать логическую схему, реализующую следующие логические функции:

Сделать это можно к примеру в Electronic workbench.

Вот для примера первое выполненное задание:

Hint: Для того чтобы включить условные обозначения в соответствии с отечественными ГОСТ-ами в файл настроек EWB.INI нужно добавить строку DIN = ON

На этом первая часть статьи заканчивается. Надеюсь, что она была не слишком утомительной. Все вышеописанное необходимо для понимания принципов работы с сигналами в электрических схемах. В следующей статье будут рассмотрены способы минимизации логических функций, понятие абстрактного автомата и пример синтеза RS-триггера.

Источник

Методические указания к выполнению ЛПЗ по Основам электроники и цифровой схемотехники

ОТДЕЛЕНИЕ Ресурсный центр Транспорта. Москва, ул. Басовская, 12 ПЦК (КМК) по укрупненной группе СПО/НПО 230000 Информатике и вычислительная техника

Зам. директора по УМР

МЕТОДИЧЕСКИЕ УКАЗАНИЯ ПО ПРОВЕДЕНИЮ

ЛАБОРАТОРНЫХ И ПРАКТИЧЕСКИХ РАБОТ

Дисциплина (Профессиональный модуль)

ОП.03 Основы электроники и цифровой схемотехники

для профессии 230103.04 Наладчик аппаратного и программного обеспечения

Разработчик(и): Плаксо Виктор Александрович, преподаватель

Методические рекомендации рассмотрены и одобрены на заседании ПЦК (КМК) по укрупненной группе СПО/НПО 230000 Информатика и вычислительная техника

протокол №___ от «__»_______ 201_ г. Председатель ПЦК_____Сивцова Е.Г.

1. Пояснительная записка

2. Правила проведения лабораторных и практических работ

3. Паспорт фонда оценочных средств

4. Состав КОС для текущего контроля знаний, умений обучающихся по учебной дисциплине/ разделам

5. Лабораторная работа №1 Ознакомление с передатчиками электрических сигналов

6. Практическая работа №1 «Определение значения логической функции и составление таблиц истинности и временных диаграмм»

7. Практическая работа №2 «Минимизация булевых функций. Метод непосредственных преобразований»

8. Практическая работа №3 «Решение задач по выполнению условий, с дальнейшим построением схем логических функций»

9. Практическая работа №4 «Исследование работы триггерных схем»

10. Практическая работа №5 «Исследование работы регистров хранения и сдвига»

11.Практическая работа №6 «Исследования работы двоичных и двоично — десятичных счетчиков»

12. Практическая работа №7 «Исследование работы дешифраторов и шифраторов. Реализация логических функций на дешифраторах»

13. Практическая работа №8 «Исследование работы мультиплексоров и демультиплексоров»

14. Практическая работа №9 «Исследование работы сумматоров»

15. Лабораторная работа №2 «Исследование работы цифро-аналогового преобразователя (ЦАП)»

16. Лабораторная работа №3 «Исследование работы оперативного запоминающего устройства»

17. Критерии оценки лабораторных и практических работ

18. Информационное обеспечение обучения

19. Список литературы

1. Пояснительная записка

Дисциплина «Основы электроники и цифровой схемотехники» входит в цикл общепрофессиональных дисциплин для профессии 230103.04 Наладчик аппаратного и программного обеспечения. Данные методические рекомендации предназначены для учащихся, изучающие данную дисциплину, и включает в себя три лабораторных работы и девять практических работ.

Данные методические рекомендации входят в состав контрольно-оценочных средств по дисциплине и предполагают формирование у учащихся знаний и умений в области электроники и схемотехники.

2. Правила проведения практических занятий

1.Обучающийся должен подготовить ответы на теоретические вопросы к ЛР или ПЗ;

2.Перед началом каждого занятия проверяется готовность обучающегося к ЛР или ПЗ;

3.После завершения ЛР или ПЗ обучающийся должен сдать преподавателю отчет о проделанной работе, выполненной в тетради;

4.Обучающийся, пропустивший ЛР или ПЗ по уважительной или неуважительной причинам, обязан выполнить задания ЛР или ПЗ в дополнительно назначенное время.

5.Оценка за выполненные задания обучающемуся выставляется с учетом предварительной подготовки к занятию, доли самостоятельности при выполнении расчетов, точности и грамотности оформления отчета.

ФОНДА ОЦЕНОЧНЫХ СРЕДСТВ

по учебной дисциплине

Основы электроники и цифровой схемотехники

наименование учебной дисциплины

230103.04 Наладчик аппаратного и программного обеспечения

код, наименование профессии/специальности

Тема 1.1. Электровакуумные и полупроводниковые приборы

Вопросы для устной проверки знаний Лабораторн..раб. №1

Тема 1.2. Волоконно-оптические линии связи

Вопросы для устной проверки знаний

Тема 2.1. Элементная база схемотехники. Логические основы цифровой схемотехники.

Тема 2.2 Комбинационные и последовательные устройства

Вопросы для устной проверки знаний

Тема 2.3 Запоминающие устройства. Цифро-аналоговые преобразователи (ЦАП) и аналого-цифровые преобразователи (АЦП).

Вопросы для устной проверки знаний

Формируемые знания и умения:

1. идентифицировать полупроводниковые приборы и элементы схемотехники и определять их параметры

2. основные сведения об электровакуумных и полупроводниковых приборах, выпрямителях, колебательных системах, антеннах; усилителях, генераторах электрических сигналов;

3. общие сведения о распространении радиоволн;

4. принцип распространения сигналов в линиях связи;

5. сведения о волоконно-оптических линиях;

6. цифровые способы передачи информации;

7. общие сведения об элементной базе схемотехники (резисторы, конденсаторы, диоды, транзисторы, микросхемы, элементы оптоэлектроники);

8. логические элементы и логическое проектирование в базисах микросхем;

9.функциональные узлы (дешифраторы, шифраторы, мультиплексоры, демультиплексоры, цифровые компараторы, сумматоры, триггеры, регистры, счетчики);

10. цифро-аналоговые и аналогово-цифровые преобразователи.

для текущего контроля знаний, умений обучающихся

по учебной дисциплине/ разделам и темам

Материалы для преставления

Раздел 1 Тема1 «Электровакуумные и полупроводниковые приборы»

Вопросы для устного опроса по теме.

по теме (Приложение 1)

Лабораторная работа №1 «Ознакомление с передатчиками электрических сигналов»

Методическая разработка лабораторной работы (Приложение 2)

Раздел 1 Тема2 «Волоконно-оптические линии связи»

Вопросы для устного опроса по теме.

по теме (Приложение 3)

Раздел 2 Тема1 «Элементная база схемотехники. Логические основы цифровой схемотехники»

Тест по теме (Приложение 4 )

Практическая работа №1 «Определение значения логической функции и составление таблиц истинности и временных диаграмм»

Методическая разработка практического занятия (Приложение 5)

Практическая работа №2 «Минимизация булевых функций. Метод непосредственных преобразований»

Методическая разработка практического занятия (Приложение 6)

Практическая работа №3 «Решение задач по выполнению условий, с дальнейшим построением схем логических функций»

Методическая разработка практического занятия (Приложение 7)

Раздел 2 Тема2 «Комбинационные и последовательные устройства»

Вопросы для письменного опроса по теме

по теме (Приложение 8)

Практическая работа №4 «Исследование работы триггерных схем»

Методическая разработка практического занятия (Приложение 9)

Практическая работа №5 «Исследование работы регистров хранения и сдвига»

Методическая разработка практического занятия (Приложение 10)

Практическая работа №6 «Исследования работы двоичных и двоично — десятичных счетчиков»

Методическая разработка практического занятия (Приложение 11)

Практическая работа №7 «Исследование работы дешифраторов и шифраторов. Реализация логических функций на дешифраторах»

Методическая разработка практического занятия (Приложение 12)

Практическая работа №8 «Исследование работы мультиплексоров и демультиплексоров»

Методическая разработка практического занятия (Приложение 13)

Практическая работа №9 «Исследование работы сумматоров»

Методическая разработка практического занятия (Приложение 14)

Раздел 2 Тема3 «Запоминающие устройства. Цифро-аналоговые преобразователи (ЦАП) и аналого- цифровые преобразователи (АЦП)»

Вопросы для письменного опроса по теме

по теме (Приложение 15)

Лабораторная работа №2 «Исследование работы цифро- аналогового преобразователя (ЦАП)»

Методическая разработка лабораторной работы (Приложение 16)

Лабораторная работа №3 «Исследование работы оперативного запоминающего устройства и флэш- памяти»

Методическая разработка лабораторной работы (Приложение 17)

Лабораторная работа №1

Ознакомление с передатчиками электрических сигналов

Цель работы: ознакомить учащихся с передатчиками электрических сигналов.

Пояснения к работе

Для передачи электрических сигналов между двумя точками необходимо организовать замкнутую электрическую цепь, соединяющую передатчик и приемник. Очевидно, что для связи двух точек необходимо иметь по крайней мере два проводника. Сигналы оп проводам могут передаваться как в потенциальном представлении, так и в токовом.

При потенциальном представлении информативным является уровень напряжения сигнала, переданный передатчиком и полученный приемником. Передача с потенциальным представлением может быть как асимметричной, так и симметричной. При асимметричной передаче один из проводов, соединяющих узлы называют общим – его потенциал относительно земли остается более или менее постоянным. Информативным (полезным сигналом) является потенциал на сигнальном проводе относительно общего провода. Например, классическая реализация Ethernet на коаксиальном кабеле. При симметричной, или дифференциальной, или балансной, передаче оба провода являются равноправными, а информативна разность потенциалов между ними. Симметрия подразумевает совпадение характеристик цепей для обоих проводников. Примером симметричной передачи является Ethernet на витой паре.

Передаваемые по проводам сигналы могут иметь и токовое представление – здесь информативно наличие или отсутствие тока в цепи. Токовое представление при небольшой пропускной способности (до 10кбит/с) обеспечивает большую дальность связи – до нескольких километров. Примером может являться городская телефонная сеть.

Для передачи сигналов используются две основные разновидности кабеля – коаксиальный кабель и витые пары проводников. Коаксиальный кабель используется для асимметричной передачи, витая пара – для симметричной (балансной).

Кабель имеет набор параметров, распределенных по всей его длине: емкость и сопротивление изоляции проводниками, индуктивность и сопротивление проводников. Эти параметры определяют частотные свойства кабеля, а также скорость распространения электрического сигнала вдоль линии.

Важным параметром кабеля является его волновое сопротивление, называемое его характеристическим импедансом, которое является комплексной величиной и измеряется в омах. Волновое сопротивление, или импеданс, непосредственно не связано ни с активным сопротивлением проводников, которое легко измеряется омметром, ни с сопротивлением изоляции, которое измеряется мегомметром. Импеданс в основном зависит от геометрии проводников кабеля и диэлектрической проницаемости материала изоляции.

Рассмотрим процесс распространения сигнала в отрезке однородной линии (рис. 1). Пусть на конце A расположен источник сигнала, а на конце B – приемник. Одиночный импульс, посланный передатчиком, начнет распространяться вдоль линии с характерной для данного кабеля скоростью. Скорость распространения сигнала обычно лежит в пределах 60-80% от скорости света в вакууме. По мере распространения сигнала в линии происходит его затухание – часть энергии рассеивается в виде потерь. Затухание Att принято измерять в децибелах(дБ).

Где P В – мощность переданного сигнала, PA – мощность принятого сигнала, а U В и UA — напряжения в точках A и B . Значение затухания, определенного поданной формуле всегда положительное, поскольку P В P А . Затухание 6дБ соответствует падению амплитуды сигнала вдове, 20дБ – в 10 раз. Кабели могут характеризоваться и погонным затуханием дБ/м. Чем меньше затухание — тем лучше кабель. С повышением частоты затухание увеличивается. К аномалиям импеданса приводят нарушения геометрии проводников (резкие изгибы, передавливания) и изоляции, применение отрезков кабеля с разными значениями импеданса. На концах отрезка источниками отражения сигнала могут и разъемы, если их импеданс не соответствует импедансу кабеля. Соединяемые кабелем устройства должны иметь соответствующий импеданс – при этом вся энергия передатчика будет уходить в линию, а приемник получит всю энергию, дошедшую до него по линии.

Мерой степени согласованности импеданса является ослабление отраженного сигнала, или возвратные потери RL . Как и затухание этот параметр измеряется в децибелах.

Где U A — амплитуда переданного сигнала, U RA — амплитуда отраженного сигнала на конце А. Большое значение RL означает лучшее согласование кабеля с оконечными элементами линии.

Рассмотрим ситуацию, когда рядом проходят две линии связи. Причем одна используется при передачи в направлении от A к B , а другая – в обратном.

При передаче сигнала от A к B по паре 1 за сет паразитных емкостных и индуктивных связей между парами, в паре 2 наводится сигнал перекрестной помехи. Этот сигнал можно наблюдать на обоих концах кабеля. Мерой этой помехи, называемой перекрестной, является ослабление перекрестной помехи на ближнем конце – NEXT .

Где U A — амплитуда переданного сигнала, U XA — амплитуда помехи на конце А. Чем большое значение NEXT – тем лучше кабель, меньше перекрестных помех.

Для кабеля, имеющего более двух пар, параметр NEXT измеряют между всеми комбинациями пар и приводят наихудшее значение. Кроме того, параметр NEXT может быть и асимметричным – различаться при измерении с различных концов. Это относится не к отдельно взятому отрезку кабеля, а к кабельной линии, которая может состоять из нескольких отрезков и пассивных средств их соединения. Поэтому, при проверке кабельного соединения NEXT измеряется с двух концов и берется наихудшее значение.

Стандартное определение NEXT исходит из того, что в кабеле в одном направлении в одно время передача данных идет по одной паре. В случае применения многопарного кабеля, перекрестная помеха будет наводиться от нескольких источников. Для нормальной работы в таком случае должен быть запас по параметру NEXT , определяемый как

NEXT = 6 + 10* lg ( n +1),

где n – число кабельных единиц, примыкающих к той кабельной единице, для которой определяют NEXT .

Критерием возможности использования кабельного соединения для двустороннего трафика является параметр ACR – отношение затухания сигнала к ослаблению перекрестной помехи.

ACR = NEXT – Att

Параметр ACR можно трактовать как отношение сигнал/шум. Положительное значение ACR означает превышение уровня полезного сигнала над уровнем помехи. Отрицательное значение ACR означает, что полезный сигнал меньше помехи, при этом его распознавание становится проблематичным. ACR зависит от частоты и с ее повышением понижается. Частота, на которой ACR переходит через ноль в отрицательное значение, считается предельно допустимой частотой при использовании данного кабеля. Для относительно надежной работы ACR на максимальной рабочей частоте должен быть не менее +2…+4 дБ.

Рассчитать по формуле затухания Att степень затухания при известных напряжениях в точках А и В.

Программа EWB (Electronics Workbench)

Работа в лаборатории

Изучить теоретический материал по данной теме;

Изучить формулу нахождения затухания Att ;

Изучить формулу нахождения возвратных потерь RL ;

Изучить формулу нахождения ослабления перекрестной помехи на ближнем конце – NEXT ;

Изучить формулу нахождения ACR – отношения затухания сигнала к ослаблению перекрестной помехи;

На основе проведенных вычислений занести результаты в таблицу.

Практическая работа №1 «Определение значения логической функции и составление таблиц истинности и временных диаграмм»

Цель: Исследовать работу логических элементов и их комбинаций.

Структурной основой любого цифрового вычислительного устройства являются логические элементы и их комбинации. Информация, обрабатываемая цифровыми устройствами, описывается логическими переменными. Их обозначают буквами А, В и т.д., которые могут принимать значения цифр 0 и 1 двоичной системы счисления. От переменных образуются простые логические функции: инверсия (А=В) – НЕ, дизъюнкция (А+В=С) – ИЛИ, конъюнкция (С=А*В) – И, а также сложные функции ИЛИ – НЕ , И – НЕ. Наиболее удобным является способ задания функции в виде таблиц истинности логических функций. Используя два сигнала высокого и низкого уровня, например, напряжения, можно строить простые логические элементы на полупроводниковой базе.

Порядок выполнения работы.

Задание 1. Исследование работы логического элемента ИЛИ.

Соберите электрическую цепь по схеме, изображенной на рисунке 1,а. Обратите внимание на условное обозначение элемента ИЛИ (рис. 1,б). (Н1, Н2, Н3 – 10Вт, 6В ; R1, R2 – 1кОм).

Исследуйте действие элемента ИЛИ по таблице состояний (рис. 1,в). С этой целью подавайте на входы А, В сигналы 1 или 0 и наблюдайте их прохождение через элемент. Сигнал 1 соответствует наличию напряжения или горению ламп, а сигнал 0 – их отсутствию. Чтобы подать сигнал 1 на вход А элемента, соедините проводником зажим «-» источника тока с зажимом А. При этом загорятся лампы Н1 на входе и Н3 на выходе, это соответствует прохождению сигнала 1. Для подачи сигнала 1 на вход В элемента соедините проводником зажим «- » источника тока с зажимом В. При этом загорятся лампы Н2 и Н3. Подайте на входы А и В элемента сигнал 1 одновременно. Пронаблюдайте загорание всех ламп. Таким образом проверяют таблицу состояний, т.е. зависимость появления сигнала 1 на выходе элемента ИЛИ от наличия и комбинации входных сигналов.

Задание 2. Исследование работы логического элемента НЕ.

Соберите электрическую цепь по схеме, изображенной на рисунке 2,а. Обратите внимание на условное обозначение логического элемента НЕ. (Н1 – 10Вт, 6В ; Н2 – 2Вт, 3В ; R1, R2 – 1кОм).

Исследуйте действие логического элемента. С этой целью подайте сигнал 1 на вход А элемента, т.е. подведите напряжение на базу транзистора. Для этого соедините проводником зажим «+» источника с зажимом А элемента и проследите за горением ламп.

Проверьте на опытах таблицу состояний элемента НЕ (рис. 2,в). Запишите вывод о наличии сигнала на выходе при наличии (сигнал 1) или отсутствии (сигнал 0) сигнала на входе.

Задание 3. Исследование работы логического элемента И.

Соберите электрическую цепь по схеме, изображенной на рисунке 3,а. Обратите внимание на условное обозначение элемента (рис. 3,б). (Н1 и Н2 — 1Вт, 6В ; Н3 – 2Вт, 3В ; R1, R2 – 1кОм).

Исследуйте действие логического элемента по таблице состояний (рис. 3,в). С этой целью подайте сигнал 1 на вход А элемента, т.е. подведите напряжение на базу транзистора V 1, соединив зажим «-» источника тока с зажимом А элемента. Обратите внимание на лампы Н2 и Н3. Отметьте, какая из них горит.

Подайте сигнал 1 на вход В элемента, т.е. соедините проводником зажим «-» источника тока с зажимом В элемента. Обратите внимание на лампы Н1 и Н3. Какая из них горит?

Подайте сигнал 1 на оба входа элемента и обратите внимание на горение ламп Н1, Н2, Н3. Таким образом, вы проверили на опытах таблицу состояний.

Запишите выводы о наличии сигнала 1 на выходе элемента при наличии или отсутствии его на входах.

Задание 4. Исследование работы комбинации логических элементов ИЛИ – НЕ.

Соберите электрическую цепь по схеме, изображенной на рисунке 4,а. Обратите внимание на условное обозначение комбинации элементов (рис. 4,б). (Н1, Н2 – 10Вт, 12В; Н3 – 2Вт, 3В; R 1 – 2 кОм, R 2 – 1кОм).

Исследуйте работу комбинации логических элементов по таблице состояний (рис. 4,в).

Подайте сигнал 1 на вход А, т.е. подведите напряжение на зажим А путем его соединения с зажимом «+» источника тока. Наблюдайте за горением ламп.

Аналогичным образом подайте сигнал 1 на вход В элемента и снова наблюдайте за горением ламп.

Подайте одновременно сигнал 1 на оба входа элемента и снова пронаблюдайте за горением ламп. Таким образом вы проверили таблицу состояний.

Запишите вывод о наличии сигнала 1 на выходе элемента при наличии или отсутствии его на входах.

Задание 5. Исследование работы комбинаций логических элементов.

Составьте таблицу истинности для данной схемы.

Повторите для других комбинаций логических элементов.

Практическая работа №2 «Минимизация булевых функций. Метод непосредственных преобразований»

Определить МДНФ логической функции устройства.

Составить таблицу соответствия (истинности) функции.

Перевести логическую функцию от табличной к аналитической форме в виде ДСНФ

Найти МДНФ различными методами.

прямым (алгебраическим) преобразованием;

усовершенствованным методом Квайна (Квайна-Маккласки);

методом карт Карно;

методом неопределенных коэффициентов;

Составить алгоритм метода минимизации

2.1 Составить содержательный (словесный) алгоритм минимизации функции, разработать граф-схему алгоритма, разработать логическую схему алгоритма в нотации Ляпунова для метода Квайна.

2.2 Составить содержательный (словесный) алгоритм минимизации функции, разработать граф-схему алгоритма, разработать логическую схему алгоритма в нотации Ляпунова для метода минимального покрытия Петрика.

2.3 Разработать рабочие программы по алгоритмам.

Синтез схемы логического устройства.

3.1 Выполнить синтез схемы по ДСНФ и МДНФ в базисе Буля с использованием двухвходовых логических элементов и интегральных микросхем серии 155.

3.2 Функцию МДНФ в базисе Буля полученную в первом задании представить в базисах Шеффера и Пирса.

Обосновать выбор базиса по формулам МДНФ.

3.4 Реализовать в выбранном базисе логическую схему.

4.1 Составить таблицу соответствия (истинности) функции.

Составим таблицу истинности для заданной функции F(X1,X2,X3,X4).

Матрицу ДСНФ получают путем удаления тех строк, где функция равна нулю. Для нашего случая получим:

4.2Перевести логическую функцию от табличной к аналитической форме в виде ДСНФ .

Переведем логическую функцию от табличной к аналитической форме в виде ДСНФ.

F(X1X2X3X4) = X1X2X3X4 V X1X2X3X4 V X1X2X3X4 V X1X2X3X4 V X1X2X3X4

V X1X2X3X4 V X1X2X3X4 V X1X2X3X4 V X1X2X3X4.

4.3 Метод эквивалентных преобразований.

В основе метода минимизации булевых функций эквивалентными преобразованиями лежит последовательное использование законов булевой алгебры. Метод эквивалентных преобразований целесообразно использовать лишь для простых функций и для количества логических переменных не более 4-х. При большем числе переменных и сложной функции вероятность ошибок при преобразовании возрастает.

Проведем прямое алгебраическое преобразование, используя закон неполного склеивания.

F(X1X2X3X4) = X1X2X3X4 V X1X2X3X4 V X1X2X3X4 V X1X2X3X4 V X1X2X3X4 V

V X1X2X3X4 V X1X2X3X4 V X1X2X3X4 V X1X2X3X4 =

= (X1X2X3X4 V X1X2X3X4) V (X1X2X3X4 V X1X2X3X4)V(X1X2X3X4 V X1X2X3X4) V

V (X1X2X3X4 V X1X2X3X4) V (X1X2X3X4 V X1X2X3X4)V(X1X2X3X4 V X1X2X3X4) V

V (X1X2X3X4 V X1X2X3X4) V (X1X2X3X4 V X1X2X3X4)V(X1X2X3X4 V X1X2X3X4) V

V (X1X2X3X4 V X1X2X3X4) V (X1X2X3X4 V X1X2X3X4) =

= X1X2X4 V X1X2X3 V X1X3X4 V X2X3X4 V X1X3X4 V X2X3X4 V X1X2X4 V

V X1X2X3V X2X3X4 V X1X2X3 V X1X3X4 =

= (X1X2X3 V X1X2X3 V X1X3X4 V X1X3X4) V X1X2X4 V

V (X1X2X3 V X1X2X3 V X2X3X4 V X2X3X4) V X1X2X4 V

V (X1X3X4 V X1X3X4 V X2X3X4 V X2X3X4) =

= X1X3 V X2X3 V X3X4 V X1X2X4 V X1X2X4.

Дальнейшее преобразование невозможно. Полученную функцию можно немного упростить с помощью вынесения за скобки общих переменных.

Практическая работа №3 «Решение задач по выполнению условий, с дальнейшим построением схем логических функций»

План решения

Обозначить простые высказывания, входящие в условие задачи, буквами (А, В, С,…).

Используя логические связи между простыми высказываниями, составить сложные высказывания (условия задачи).

Перемножить сложные высказывания, приравняв произведение к 1.

Построить таблицу истинности.

Записать ответ (выбрать из таблицы истинности при каких значениях простых высказываний логическая функция принимает значение истина).

Задача 1

Задача 2

Практическая работа №4 «Исследование работы триггерных схем»

Цель работы:

Закрепление теоретического материала путем макетирования и экспериментального исследования элементов ЭВМ, а также развитие навыков по сборке и проверке функционирования цифровых схем с помощью современной измерительной аппаратуры.

Триггеры имеют два устойчивых состояния. Эти состояния определяются по логическим уровням на выходах триггера. Триггер снабжается двумя выходами: прямым Q и инверсным

Триггеры могут иметь входы различного типа:

R (от англ. RESET) – раздельный вход установки в состояние 0;

S (от англ. SET) – раздельный вход установки в состояние 1;

К – вход установки универсального триггера в состояние 0;

J – вход установки универсального триггера в состояние 1;

V — вход разрешения;

С — синхронизирующий вход;

D — информационный вход;

Т — счетный вход

и некоторые другие.

Обычно название триггера дают по имеющимся у него входам: RS-триггер, JK-триггер, D-триггер и др.

По способу записи информации триггеры подразделяются на асинхронные и синхронные. В асинхронных триггерах состояние на выходе изменяется сразу же после изменения сигнала на информационных входах. В синхронных триггерах для передачи сигнала с информационных входов на выходы требуется специальный синхронизирующий импульс. Синхронные триггеры подразделяются на триггеры со статическим управлением и триггеры с динамическим управлением. В триггерах с динамическим управлением передача сигнала с информационных входов на выходы осуществляется по фронту или по спаду синхронизирующего импульса.

Триггеры относятся к цифровым автоматам. В отличие от комбинационных схем состояние на выходе триггера в данный момент времени определяется не только состояниями на входах триггера в этот же момент времени, но и предыдущим состоянием триггера. Цифровые автоматы, к которым относятся триггеры, иногда называют последовательными схемами.

Триггеры строились по самым разнообразным электрическим схемам. В последнее время триггеры обычно конструируют, используя логические элементы.

Рассмотрим два варианта RS-триггера: RS-триггер с прямыми входами и RS-триггер с инверсными входами. Установка триггера в нужное состояние осуществляется подачей уровня логической «1» на соответствующий вход для триггера с прямыми входами и подачей сигналов логического «0» для триггера с инверсными входами. Наибольшее распространение получили RS-триггеры, построенные на логических элементах 2И-НЕ или 2ИЛИ-НЕ. На рисунке 1.36,а приведена функциональная схема RS-триггера с инверсными входами на двух логических элементах 2И-НЕ, а на рисунке 1.36,б – его условное обозначение на принципиальных схемах.

RS- триггер с прямыми входами можно получить, имея в наличии два логических элемента 2ИЛИ-НЕ. Триггер получается путем соединения выхода первого логического элемента с одним из входов второго и соединения выхода второго логического элемента с одним из входов первого. Как видно из получившейся схемы (рис. 1.37,а), по отношению к логическим элементам триггер симметричен. По этой причине не имеет принципиального значения, выход какого из элементов считать прямым выходом триггера. Допустим, что прямым выходом триггера является верхний вывод. Определим, какой из входов триггера является входом R, а какой – входом S. Вспомним, что активным логическим уровнем для элементов ИЛИ-НЕ является уровень логической единицы, т.е. если на входе элемента 2ИЛИ-НЕ действует логическая «1», то на выходе будет «0». Зная, что вход R – это вход установки триггера в нулевое состояние, приходим к выводу, что входом R в данном случае будет верхний вход RS-триггера. Функциональная схема RS-триггера с прямыми входами на двух логических элементах 2ИЛИ-НЕ и его условное обозначение на принципиальных схемах приведены соответственно на рисунках 1.37а,б.

Работу RS-триггера можно описать различными способами: аналитически с помощью формулы; с помощью таблицы, в которой записываются состояния на входах и выходах триггера в различные моменты времени; с помощью временных диаграмм. На временной диаграмме показывают, как меняются сигналы на выходах триггера при изменении сигналов на его входах. Рассмотрим временную диаграмму работы RS-триггера с прямыми входами. Для RS-триггера нужно показать 4 графика (рис. 1.38).

Пусть на входах R и S установлены пассивные для элементов ИЛИ-НЕ уровни логического нуля (пассивные логические уровни не могут изменить состояние триггера) и пусть триггер находится в единичном состоянии, т.е. на выходе Q уровень логической единицы. Подадим на вход R в момент времени t1 уровень логической единицы. Для анализа работы RS-триггера, как и любого цифрового устройства, воспользуемся понятием активного логического уровня. Это существенно облегчает анализ работы схемы. Если на одном входе логического элемента действует активный логический уровень, то нет необходимости анализировать логические состояния на других входах элемента. Т.к. в момент времени t1 на ходе R элемента DD1.1 действует активный логический уровень, то на выходе этого элемента, как следует из таблицы истинности, будет уровень логического нуля. На входах Х1 и Х2 элемента DD1.2 уровни логического нуля и, следовательно, на выходе этого элемента уровень логической единицы. Мы видим, что состояние триггера изменилось с единичного на нуле-вое. В момент времени t в 2 установим на входе R уровень логического нуля. На входе Х2 элемента DD1.1 уровень логической единицы и поэтому состояние триггера не изменится: на выходе Q логический нуль, а на выходе Q – логическая единица. В момент времени t3 на входе S установим уровень логической единицы, т.е. на входе Х2 элемента DD1.2 будет активный логический уровень и на выходе этого элемента установится уровень логического нуля. На входах Х1 и Х2 элемента DD1.1 будут уровни логического нуля, а на выходе этого элемента – уровень логической единицы. Триггер перешел из нулевого состояния в единичное. В момент времени t4 подадим на вход S уровень логического нуля и, проведя аналогичный анализ, увидим, что состояние триггера в момент времени t4 не изменится. В момент времени t5 подадим на вход S уровень логической единицы. Проведя аналогичный анализ, увидим, что состояние триггера не изменилось: на прямом выходе Q – уровень логической единицы, а на инверсном – уровень логического нуля. В момент времени t6 установим уровень логической единицы на входе R. В этом случае на выходе Q появится уровень логического нуля, и уровень логического нуля останется на выходе Q. В момент времени t7 установим на входах R и S одновременно уровень логического нуля. Состояние триггера в этом случае будет неопределенным. Может оказаться, что на выходе Q логическая единица, а на выходе Q логический нуль, или наоборот. Поэтому в устройствах цифровой техники одновременную подачу активных логических уровней на входы R и S триггера запрещают. Такой запрет делают не потому, что триггер выйдет из строя, а потому, что состояние триггера неоднозначно после одновременного снятия уровней логической единицы на входах R и S. В момент времени t8 подадим на вход R напряжение логической единицы, в результате чего на прямом выходе триггера получим напряжение логического нуля.

Рассмотренные триггеры относятся к так называемым асинхронным триггерам. В асинхронных триггерах состояние на выходе изменяется в момент поступления сигналов на информационные входы. В синхронных триггерах для передачи сигнала с информационных входов на выход требуется специальный синхронизирующий импульс.

Синхронные триггеры подразделяются на триггеры со статическим управлением и триггеры с динамическим управлением. В триггерах с динамическим управлением передача сигналов с информационных входов на выходы осуществляется либо по фронту синхронизирующего импульса, либо по спаду синхронизирующего импульса.

На рисунках 1.39,а,в приведены функциональные схемы синхронного RS-триггера с прямыми входами, а условное обозначение этих триггеров на принципиальных схемах показано на рисунке 1.39,б.

Рассмотрим функциональную схему синхронного RS-триггера, приведенную на рисунке 1.39а. При С=0 на входах R, S асинхронного триггера на элементах DD1.1 и DD1.2 действуют сигналы логического нуля (логический нуль является пассивным логическим уровнем для логических элементов 2ИЛИ-НЕ), поэтому при любых комбинациях сигналов на входах R, S синхронного RS-триггера состояние триггера не меняется. При С=1 рассмотренный синхронный RS-триггер работает точно так же, как рассмотренный чуть раньше асинхронный RS-триггер с прямыми входами. Рассмотренный только что синхронный RS-триггер относится к триггерам со статическим управлением.

На рисунках 1.40,а и 1.41,а приведены функциональные схемы синхронных RS-триггеров с динамическим управлением, а их условные обозначения на принципиальных схемах соответственно на рисунках 1.40,б и 1.41,б. Если в

обозначении синхронного RS-триггера с динамическим управлением стрелочка на входе С направлена к триггеру, то передача сигналов с информационных входов на выходы происходит по фронту импульса, а если стрелочка направлена от обозначения триггера, то передача сигнала осуществляется по спаду импульса.

Рассмотрим синхронный RS-триггер с динамическим управлением, схема которого приведена на рисунке 1.40,а. Проанализировав функциональную схему синхронного RS-триггера с динамическим управлением, убедимся в том, что состояние триггера не меняется как при изменении сигналов на входах S и R при С=0, так и при С=1, если триггер переключился по фронту синхронизирующего импульса. При C=0 на выходах элементов DD2.1, DD2.2 будут сигналы логической единицы, и состояние на выходе триггера изменяться не будет при любых изменениях сигналов на входах R и S. Установим на инверсном входе S уровень логического нуля, на инверсном входе R уровень логической единицы, и сигнал на входе С изменим с логического нуля на логическую единицу. На выходе элемента DD2.1 появится сигнал логического нуля и триггер перейдет в единичное состояние, или состояние триггера не изменится, если он находился в единичном состоянии. Оставляя на входе С сигнал логической единицы, перевести триггер в нулевое состояние не удается. Для перевода триггера в противоположное состояние обязательно необходимо подать синхронизирующий импульс.

В синхронных RS-триггерах со статическим управлением остается неоднозначность состояния на выходе триггера, если с входов R, S одновременно убирать активные уровни сигналов. Для устранения неоднозначности в схему синхронного RS-триггера добавляют логический элемент «НЕ». Получившийся триггер является D-триггером со статическим управлением. Функциональная схема этого триггера приведена на рисунке 1.42,а, а его условное обозначение на принципиальных схемах – на рисунке 1.42,б.

При С=0 состояние триггера изменяться не будет какой бы ни был сигнал на входе D, т.к. на выходах элементов DD2.1, DD2.2 будут сигналы логических нулей. При С=1 и D=1 на выходе элемента DD2.1 появится сигнал логического нуля, а на прямом выходе D-триггера – сигнал логической единицы. При С=1 и D=0 сигнал логического нуля появится на выходе элемента DD2.2, на инверсном выходе D-триггера установится логическая единица, а на прямом выходе –логический нуль. Таким образом, D-триггер воспринимает информацию с входа D и передает ее на выход Q при C=1, и затем хранит ее сколько угодно долго (пока подключен источник питания) при С=0. Т.е. мы имеем ячейку памяти для хранения 1 бита информации.

На рисунке 1.43,а приведен еще один вариант схемы D-триггера со статическим управлением. Условное обозначение обоих этих триггеров одинаковое.

Временная диаграмма работы D-триггера со статическим управлением приведена на рисунке 1.44.

Из диаграммы следует, что передача информации с входа D на выход Q осуществляется во время действия синхронизирующего импульса. Счетный триггер из данного триггера путем соединения инверсного выхода с входом D получить нельзя. Из D-триггера можно легко получить DV-триггер. Вместо логических элементов 2И-НЕ используют логические элементы 3И-НЕ и делают дополнительно вход разрешения V. Функциональная схема DV-триггера и его условное обозначение на принципиальных схемах показаны соответственно на рисунке 1.45,а-б.

Широко используют D-триггеры с динамическим управлением. В них передача информации с информационных входов на выходы осуществляется либо по фронту синхронизирующего импульса, либо по спаду синхронизирующего импульса. Функциональная схема D-триггера с передачей информации с входа на выход триггера по фронту синхронизирующего импульса приведена на рисунке 1.46,а, а его условное обозначение на принципиальных схемах – на рисунке 1.46,б.

При С=0 на выходах элементов DD1.3, DD1.4 будут сигналы логических единиц и состояние на выходе триггера не изменится при любых изменениях сигнала на входе D. Установим на входе D сигнал логической единицы и изменим на входе С сигнал с логического нуля на единицу. Перед подачей на вход С сигнала логической единицы на выходе элемента DD1.2 логический нуль, а на верхнем входе элемента DD1.3 логическая единица. При появлении на входе С логической единицы на выходе элемента DD1.3 установится логический нуль, а на прямом выходе триггера – логическая единица. Сигнал логического нуля подается с выхода элемента DD1.3 на нижний вход элемент DD1.1 и на верхний вход элемента DD1.4. Оставляя на входе С логическую единицу, изменим сигнал на входе D с логической единицы на нуль. На выходе элемента DD1.2 установится логическая единица, а сигналы на выходах элементов DD1.1, DD1.3 не изменятся, следовательно, не изменится состояние на выходе триггера.

При D=0 изменим сигнал на входе С с логической единицы на нуль. На выходах элементов DD1.3, DD1.4 будут логические единицы, а на прямом выходе триггера останется сигнал логической единицы. Затем изменим сигнал на входе С с логического нуля на логическую единицу. На выходе DD1.4 установится логический нуль, на инверсном выходе триггера логическая единица, а прямом выходе – логический нуль. Из анализа работы данного триггера следует, что в нем передача информации с входа D на выход Q осуществляется по фронту синхронизирующего импульса, подаваемого на вход С.

Триггеры являются составной частью счетчиков электрических импульсов. D-триггер с динамическим управлением легко превратить в счетный триггер. С этой целью необходимо инверсный выход триггера соединить с информационным входом D, а импульсы подавать на синхронизирующий вход. Схема такого соединения приведена на рисунке 1.46,в.

Находят применение двухтактные RS-триггеры (рис. 1.47,а). На рисунке 1.47,б приведена схема счетного триггера, построенного на основе двухтактного RS-триггера. Двухтактный RS-триггер состоит из двух триггеров: главного и

вспомогательного. Иногда главный триггер называют ведущим, а вспомогательный ведомым. По окончании синхронизирующего (тактового) импульса вспомогательный триггер переписывает информацию с выхода главного триггера. Используя двухтактные RS-триггеры, можно построить JK-триггер. В JK-триггере устранена неопределенность, возникающая в RS-триггере при одновременном снятии активных логических сигналов с входов R и S.

Функциональная схема JK-триггера, построенного с использованием двухтактных (двухступенчатых) RS-триггеров, приведена на рисунке 1.48,а, а его условное обозначение на принципиальных схемах – на рисунке 1.48,б.

В условных обозначениях триггеров, построенных с использованием двухтактного синхронного RS-триггера, ставят две буквы Т. Если входы J и K данного триггера соединить вместе и подать на них сигнал логической единицы, а импульсы подавать на вход С, то получим счетный триггер.

Широкое распространение получили JK-триггеры, построенные с использованием синхронных RS-триггеров с динамическим управлением. На рисунке 1.49,а приведена функциональная схема JK-триггера, переключающегося по спаду синхронизирующего импульса, а условное обозначение этого триггера на принципиальных схемах приведено на рисунке 1.49,б. Элементы DD1.1, DD1.2 образуют асинхронный RS-триггер.

Функциональная схема JK-триггера, переключающегося по фронту синхронизирующего импульса, показана на рисунке 1.50,а, а условное обозначение приведено на рисунке 1.50,б. При С=0 на выходах элементов DD2.1 и DD2.2 логические единицы и состояние RS–триггера DD3 не изменяется. Если на инверсных входах J и K логические единицы, то переключение сигнала на входе С с логического нуля на логическую единицу не изменит состояние на выходе JK–триггера.

На рисунке 1.50,в приведена схема использования JK-триггера в качестве счетного. На входы J и K подаются логические нули, а импульсы подаются на вход С. Вход С в данном случае является счетным входом Т. Частота импульсов на выходе данного счетчика в два раза меньше частоты импульсов на входе. Скважность импульсов на выходе счетчика равна двум независимо от скважности импульсов на входе счетчика.

Напомним, что триггеры относятся к цифровым автоматам. Цифровые автоматы состоят из комбинационных схем. Триггеры входят в состав счетчиков электрических импульсов, регистров, запоминающих устройств.

Порядок выполнения работы.

Задание 1. Исследование работы RS -триггера в статическом режиме.

1. Соберите схему асинхронного RS -триггера из элементов 2ИЛИ-НЕ.

2. Составьте таблицу состояний в зависимости от входных сигналов (таблица должна содержать все возможные комбинации входных сигналов):

Источник