Последовательные цифровые устройства

Цифровое устройство называется последовательным (ПЦУ), если сигналы на его выходе зависят не только от текущих значений входных сигналов, но и от состояния цифрового устройства (т.е. от предыдущих входных сигналов). В ПЦУ обязательно должны входить ячейки памяти. Ячейка памяти Т под воздействием входного сигнала изменяет своё состояние (0 или 1).

Простейший автомат – триггер.

Триггер – устройство, которое находится в одном из двух устойчивых состояний и переходит из одного в другое под воздействием входных сигналов. Для удобства триггер имеет два выхода: прямой Q и инверсный

По способу приёма информации триггеры подразделяются:

1) Асинхронные переключаются непосредственно информационными сигналами,

2) Синхронные – реагируют на информационные сигналы при наличии сигнала на специальном управляющем входе С – вход синхронизации.

Управление может быть статическим (уровнем управляющего сигнала) и динамическим (фронтом импульса управляющего сигнала).

По функциональным возможностям:

Рис.7.9.

Асинхронный триггер переключается под действием информационного сигнала (1), а синхронный под действием тактового сигнала. Т- триггер иногда называют счётным.

2) D – триггер (триггер задержки).

Имеет один информационный вход и вход синхронизации. Триггер передаёт на выход значение входного сигнала, но с задержкой пока не приходит тактовый импульс.

Рис.7.10.

На рис.7.11 показано условное обозначение асинхронного RS — триггера с прямыми входами, реализация на базовых элементах 2ИЛИ-НЕ и таблица истинности. Функциональное уравнение имеет вид

Если RS — триггер реализовать на четырёх элементах 2И-НЕ, то получается RS — триггер с инверсными входами. Синхронный RS — триггер его реализация, а также таблица истинности приведены на рис.7.12.

Рис.7.11.

Рис.7.12.

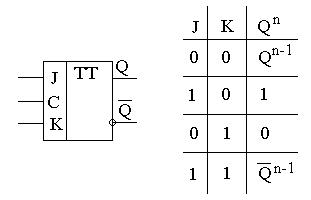

4). JK-триггер (универсальный). Обозначение триггера таблица состояний приведены на рис.7.13.

Рис.7.13.

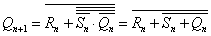

Функциональное уравнение для него есть

Триггер переключается тактовым импульсом при наличии логической единицы на обоих информационных входах. При остальных комбинациях повторяет RS — триггер. При объединении JK- входов превращается в Т — триггер. При объединении с одновременным инверсным выходом превращается в D — триггер.

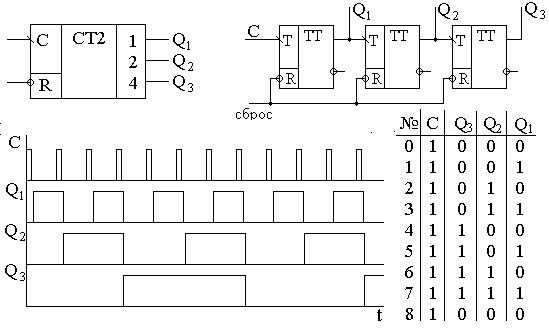

7.5. Счётчики.

Счётчик — последовательное цифровое устройство, обеспечивающее хранение слова информации и выполнение над ним микрооперации счёта (т.е. изменения числа на ±1). В зависимости от направления счёта счётчики разделяют на суммирующие, вычитающие и реверсивные. По способу организации схемы переноса – с последовательным, параллельным и параллельно-последовательным переносом. По наличию синхронизации – синхронные и асинхронные счётчики. Счётчики обычно строят на Т – триггерах. Однако могут применятся и D — триггеры и JK — триггеры.

Суммирующие двоичные счётчики.

В счётчике с n триггерами число возможных состояний 2 n . Каждому состоянию счётчика соответствует число в счётной последовательности от 0 до2 n -1 при последовательной подаче на вход С единицы. Исходное (начальное) состояние счётчика устанавливается подачей сигнала по шине «установка 0». После подачи 2 n импульсов на вход С счётчик снова устанавливается в нулевое положение.

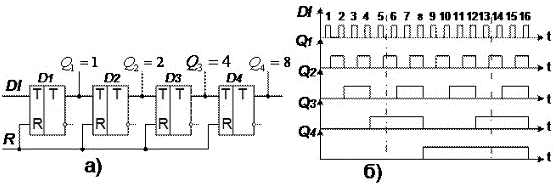

Рис.7.14.

В суммирующем счётчике (рис.7.14) при работе происходит суммирование предыдущего значения счётчика с единицей. Рассмотренный счётчик называется счётчиком с последовательным переносом. Сигнал для счёта подаётся на вход самого младшего разряда, каждый последующий разряд переключается задним фронтом сигнала с предыдущего разряда, все Т — триггеры соединены последовательно. При этом время задержки переносов растёт с ростом числа разрядов в счётчике, ограничивая его быстродействие.

Это устраняется в счётчике с параллельным переносом, где все триггеры срабатывают одновременно по счётному входному импульсу. При этом схема усложняется, поскольку требуются элементы «И» с большим числом входов (рис 7.15).

Рис.7.15.

Поэтому при построении многоразрядных счётчиков используются схемы с параллельно-последовательным переносом, когда внутри группы триггеров организуется параллельный перенос, а между группами – последовательный (рис.7.16).

Рис.7.16.

Вычитающий счётчик с приходом каждого счётного импульса предыдущий результат уменьшает на 1. Вход каждого последующего триггера соединяется с инверсным выходом предыдущего.

Рис.7.17.

Для построения десятичного счётчика используют четырёх разрядныё двоичный счётчик, число состояний которого уменьшают с 16 до 10 с помощью внешнего или внутреннего КЦУ.

Источник

Способы описания последовательных цифровых устройств

5 Цифровые устройства последовательностного типа

Цифровые устройства последовательностного типа или цифровые автоматы с памятью — это электронные цифровые устройства, логические значения на выходах которых определяются не только совокупностью логических сигналов на входах в данный момент времени, но и состоянием внутренних элементов памяти по результатам его предшествующей работы. Запоминание предшествующих состояний выполняется при помощи триггеров и регистров памяти.

Типичными примерами логических автоматов с памятью являются счётчики импульсов и сдвиговые регистры.

Триггеры — это электронные устройства, обладающие двумя устойчивыми состояниями равновесия и способные скачком переходить из одного устойчивого состояния в другое под воздействием внешних управляющих сигналов.

Состояние называется устойчивым, если слабое внешнее воздействие не нарушает этого состояния. Для перехода триггера из одного состояния в другое необходимо, чтобы входной сигнал превысил пороговое значение.

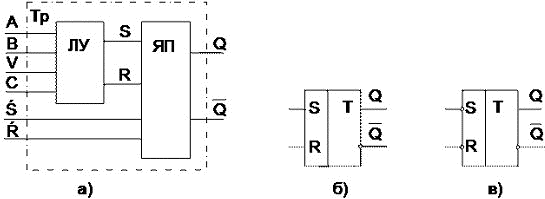

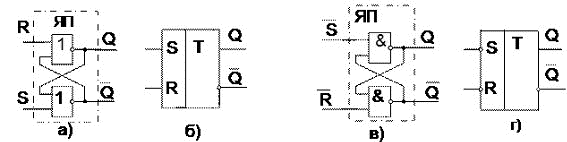

Триггер Тр (Рисунок 41) в общем случае можно представить как устройство, состоящее из ячейки памяти ЯП и логического устройства (ЛУ) управления, преобразующего входную информацию в комбинацию сигналов, под воздействием которых ЯП принимает одно из двух устойчивых состояний.

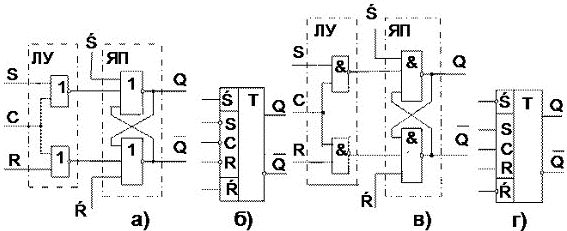

Рисунок 41 Обобщённое устройство триггера а):

RS-триггеры с прямыми б) и инверсными статическими входами в).

Информационные сигналы поступают на входы A и В ЛУ и преобразуются в сигналы, поступающие на внутренние входы S и R ЯП. Процесс преобразования информационных сигналов осуществляется под воздействием сигналов, подаваемых на вход V разрешения приёма информации и вход C синхронизации, обеспечивающей тактируемый приём информации.

При наличии входа C триггер называют синхронным, а при его отсутствии — асинхронным. Управляющие сигналы на асинхронный триггер воздействуют непосредственно с началом своего появления на их входах, а в синхронных — только с приходом сигнала на входе C.

Триггеры могут иметь статические или динамические входы. Как статические, так и динамические входы могут быть прямыми или инверсными.

Входы называются статическими, если они имеют непосредственную связь с источником входных сигналов. Сигналом для управления статическим триггером с прямыми статическими входами является уровень лог. «1», а для управления триггером с инверсными входами — уровень лог «0».

Входы называются динамическими, если они соединены с источником входных сигналов через развязывающие цепи: магнитные, электронные или RC-цепи. Они реагируют только на перепады входных сигналов. Если срабатывание триггера происходит при изменении входного сигнала от «0» к «1», то входы называются прямыми, а если при изменении сигнала от «1» к «0», то — инверсными.

Входы Ś и Ŕ называются входами асинхронной установки триггера. Они предназначены для подачи приоритетных сигналов установки триггера в исходное состояние (0 или 1) в начале цикла работы независимо от воздействия информационных сигналов, то есть в обход схемы управления.

Наибольшее применение находят триггеры с раздельным запуском, которые называются RS-триггерами. Их условное графическое обозначение приведено на рисунке 41. В простейшем RS-триггере информационные сигналы подаются непосредственно на входы S и R ячейки памяти.

Входы, на которые подаются запускающие импульсы, называются установочными. Буквой S (Set — установка) обозначают вход, на который подаётся сигнал, устанавливающий триггер в единичное состояние (Q=1,

RS-триггеры применяются как самостоятельно, так и в составе других более сложных триггеров, а также входят в состав регистров и счётчиков.

RS-триггеры на логических элементах

Функционирование логических устройств последовательностного типа описывается таблицами переходов, которые отличаются от таблиц истинности тем, что в них учитываются только результативные переходы, когда изменение комбинации сигналов на входе приводит к изменению выходного состояния. Однако таблица переходов может быть сведена к таблице истинности, если состояние внутренних элементов памяти считать входными сигналами.

Полная таблица функционирования (таблица истинности) приведена на рисунке 42,а, в которой предыдущее состояние триггера Qn до подачи входных сигналов является одним из входных сигналов. Выходное состояние триггера после подачи входных сигналов обозначено символом Qn+1. Таблица переходов триггера приведена на рисунке 42,б.

| Qn | S | R | Qn+1 | Режим работы |

|---|---|---|---|---|

| 0 | 0 | 0 | 0 | Хранение «0» |

| 0 | 0 | 1 | 0 | Подтверждение «0» |

| 0 | 1 | 0 | 1 | Установка в «1» |

| 0 | 1 | 1 | ф | Запрещённое состояние |

| 1 | 0 | 0 | 1 | Хранение «1» |

| 1 | 0 | 1 | 0 | Сброс в «0» |

| 1 | 1 | 0 | 1 | Подтверждение «1» |

| 1 | 1 | 1 | ф | Запрещённое состояние |

| S | R | Qn+1 |

|---|---|---|

| 0 | 0 | Qn |

| 0 | 1 | 0 |

| 1 | 0 | 1 |

| 1 | 1 | ф |

Рисунок 42 Таблица истинности а) и таблица переключений RS-триггера б)

Таблица истинности позволяет применить рассмотренную выше методику синтеза логических устройств комбинационного типа для синтеза устройств последовательностного типа, в том числе и RS-триггеров.

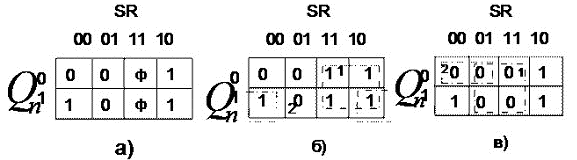

Для минимизации структурной формулы RS-триггера заполним карту Карно, приведённую на рисунке 43,а.

Рисунок 43 Карты Карно для минимизации структурной формулы RS-триггера

В соответствии с теорией минимизации неопределённых логических функций, для определения прямого значения функции Qn+1 неопределённые значения карты Карно «ф» (Рисунок 43,а) заменим «1» (Рисунок 43,б), а для определения инверсного значения

Минимизированные значения функций Qn+1 и

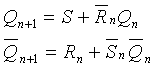

Рисунок 44 RS-триггеры: а), б) — на логических элементах ИЛИ-НЕ,

в), г) — на логических элементах И-НЕ.

Для реализации триггера на элементах ИЛИ-НЕ проинвертируем функцию

Структурная схема триггера, полученная в соответствии с этим выражением, приведена на рисунке 44,а. В структурной формуле установочные сигналы S и R представлены в прямом коде, следовательно исполнительными значениями сигналов являются уровни лог. «1», то есть триггер на элементах ИЛИ-НЕ имеет прямые статические входы.

Для реализации триггера на элементах И-НЕ дважды проинвертируем функцию Qn+1:

Как следует из полученного выражения, исполнительными значениями сигналов здесь являются лог. «0», поэтому RS-триггер на элементах И-НЕ имеет инверсные статические входы. Структурная схема триггера и его УГО приведены на рисунках 44,в,г.

При разработке цифровых схем, в которые входят RS-триггеры, необходимо учитывать наличие запрещённого состояния входных сигналов для RS-триггеров на элементах ИЛИ-НЕ S=R=1, а для RS-триггеров на элементах И-НЕ

Если в разрабатываемой схеме такое сочетание входных сигналов в принципе возможно, то эту ситуацию необходимо исключить путём включения во входную цепь дополнительных логических элементов, или использовать другие типы триггеров, не имеющих запрещённого состояния.

Рассмотренные RS-триггеры являются асинхронными поскольку управляющие сигналы воздействуют на триггер непосредственно с началом своего появления на их входах.

В устройствах современной цифровой техники, для исключения опасных состязаний входных сигналов, срабатывание всех узлов и элементов в каждом такте должно происходить строго одновременно. Для достижения этой цели применяется жёсткая синхронизация с помощью специальных синхроимпульсов. Для работы в схемах с синхронизацией режима разработаны синхронные RS-триггеры.

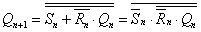

Рисунок 45 Синхронные RS-триггеры: — а) на элементах ИЛИ-НЕ, — в) на элементах И-НЕ и их УГО б), и г).

Особенностью синхронного триггера является то, что ввиду наличия в схеме управления инвертирующих элементов, происходит изменение исполнительного значения управляющих сигналов по сравнению с асинхронными.

Синхронные RS-триггеры имеют три входа: S, R и C. Применение синхронизации не устраняет неопределённое состояние триггера, возникающее при одновременной подаче единичных сигналов на все три входа. Поэтому условием нормального функционирования является следующее неравенство:

Кроме трёх основных входов, синхронные RS-триггеры снабжаются ещё входами асинхронной установки состояния триггера — Ś и Ŕ. Они предназначены для подачи приоритетных сигналов установки триггера в исходное состояние (0 или 1) в начале цикла работы независимо от воздействия сигналов на входах S и R, то есть в обход схемы управления.

По своему воздействию на состояние триггера входы Ś и Ŕ являются самыми главными и поэтому на УГО отделяются от остальных сигналов горизонтальной линией.

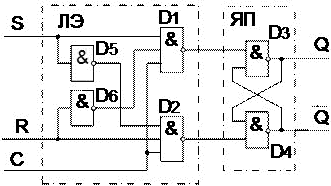

RS-триггеры S, R и E-типов

В отличие от обычных RS-триггеров у триггеров S, R и E-типов комбинация сигналов S=R=1 не является запрещённой. При разнополярных сигналах алгоритм работы триггеров S, R и E-типов такой же, как и у обычных RS-триггеров, но при S=R=1 триггер S-типа переключается в «1», триггер R-типа в «0», а триггер E-типа не изменяет своего состояния (Рисунок 45).

Рисунок 46 RS-триггер Е-типа

Схема работает как обычный RS-триггер, но при подаче сигналов S=R=1 вентили D5 и D6 обеспечивают закрытое состояние элементов D1 и D2, поэтому выходное состояние триггера Q остаётся без изменения.

Если исключить из схемы Рисунок 46 элемент D6, то при подаче на вход сигналов S=R=1 блокируется только элемент D2, на выходе которого устанавливается «1», а на выходе D1 формируется «0». Эти сигналы устанавливают триггер в состояние Q=1, или подтверждают его, если до подачи сигналов S=R=1 триггер находился в состоянии Q=1. Такой триггер называется RS-триггером S-типа.

Если исключить из схемы Рисунок 46 элемент D5, оставив элемент D6, то при подаче на вход сигналов S=R=1 блокируется только элемент D1, поэтому триггер устанавливается в состояние Q=0 или подтверждают его, если до подачи сигналов S=R=1 триггер находился в состоянии Q=0. Такой триггер называется RS-триггером R-типа.

5.1.2 D-триггеры (триггеры задержки)

D-триггеры — это электронные устройства с двумя устойчивыми выходными состояниями и одним информационным входом D.

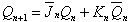

Характеристическое уравнение триггера: Qn+1=Dn. Оно означает, что логический сигнал Qn+1 повторяет значение сигнала, установленное на входе триггера в предшествующий момент времени.

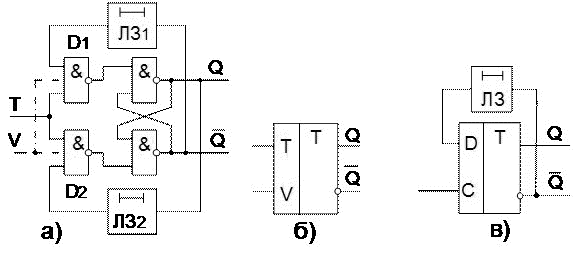

Благодаря включению элемента D1 на входы RS-триггера поступают разнополярные сигналы (Рисунок 47,а), поэтому запрещённое состояние входных сигналов исключено но время задержки распространения сигнала элемента D1 должно быть меньше, чем у элементов D2 и D3 (tзд.р1 tи.

Рисунок 50 Т-триггеры: — а) структурная схема, б) УГО TV-триггера,

в) Т-триггер на основе D-триггера.

По окончании действия тактирующего импульса.

Пусть в исходном состоянии Q=1. Сигнал T=1 откроет элемент D2, так как на втором входе D2 имеется сигнал лог «1» с выхода Q, а элемент D1 будет закрыт. Триггер переходит в состояние Q=0. Вентиль D2 остаётся открытым в течение времени tи, т.к. сигнал Q=1 будет задержан ЛЗ1 на время τз>tи. В то же время сигнал

По окончании действия тактирующего импульса элементы D1 и D2 закроются, так как потенциал входа T=0. После чего на вход элемента D1 через ЛЗ2 поступит сигнал

Роль ЛЗ в Т-триггерах выполняют логические элементы с большим временем задержки tзд.р или специальные компоненты электронных схем, например, диоды с накоплением заряда.

Кроме счётного входа Т-триггер может иметь вход разрешения V (Рисунок 50,б). Сигнал на этом входе разрешает (при V=1) или запрещает (при V=0) срабатывание триггера от поступающих на вход T сигналов. Т-триггеры, имеющие дополнительный вход V, называются TV-триггерами. Наличие входа V позволяет организовать счёт в заданном временном интервале, что существенно расширяет функциональные возможности Т-триггера.

Счётный Т-триггер может быть построен на основе D-триггера, соединив инверсный выход D-триггера со входом D, как показано на рисунке 50,в. В такой схеме каждый переход 1/0 на входе C будет приводить к переходу триггера в противоположное состояние. Например, если Qn=1, то

Таким образом, из рассмотрения принципа работы Т-триггера следует, что при Т=1 спадающий фронт сигнала на входе C переводит триггер в противоположное состояние. Частота изменения потенциала на выходе Т-триггера в два раза меньше частоты импульсов на входе C. Это свойство Т-триггеров позволяет строить на их основе двоичные счётчики. Поэтому эти триггеры и называют счётными.

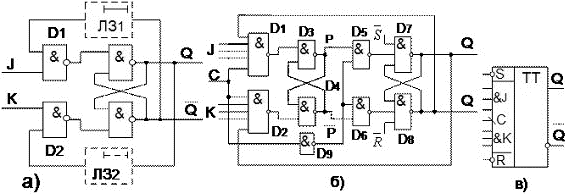

JK-триггер — это схема с двумя устойчивыми выходными состояниями и двумя входами J и K (Рисунок 51.а). Подобно RS-триггеру, в JK-триггере входы J и K — это входы установки выхода Q триггера в состояние 1 или 0. Однако, в отличие от RS-триггера, в JK-триггере наличие J=K=1 приводит к переходу выхода Q триггера в противоположное состояние. Условие функционирования JK-триггера описывается функцией:

Рисунок 51 JK-триггеры: а) асинхронные; б) тактируемые фронтом.

Триггер JK-типа называют универсальным потому, что на его основе с помощью несложных коммутационных преобразований можно получить RS и Т-триггеры, а если между входами J и K включить инвертор, то получится схема D-триггера.

Недостатком этой схемы является зависимость работы схемы от длительности тактового импульса. Импульс должен быть коротким и должен закончиться до завершения процесса переключения триггера. Для ослабления требования к длительности тактового импульса в цепи обратных связей можно включить элементы задержки, как показано на рисунке 51,а пунктиром. Однако этот путь не всегда является целесообразным.

Разработаны и применяются в основном в интегральном исполнении JK-триггеры, тактируемые фронтом тактовых импульсов, которые не чувствительны к длительности тактовых импульсов.

JK-триггеры, тактируемые фронтом, строятся по схеме MS (master-slave то есть мастер-помощник). В схеме имеется два триггера: основной D1…D4, помощник D5…D8 и цепь, разделяющая их — D9 (Рисунок 51,б).

Триггер работает следующим образом. Пусть в исходном состоянии Q=0, а

Пусть J=1, тогда с приходом тактового импульса C=1, D1 откроется, а D2 останется закрытым. Элементы D5 и D6 закроются сигналом

Несмотря на то, что на одном из входов D5 действует сигнал «1», а на одном из входов D6 — «0», они не изменят состояние вспомогательного триггера, так как на других входах элементов D5 и D6 действует сигнал лог. «0» с инвертора D9.

По окончании действия тактового импульса, появится сигнал лог. «1» на вторых входах вентилей D5, D6, а вентили D1 и D2 закроются. Так как основной триггер находится в состоянии «1», то откроется D5 и информация запишется во вспомогательный триггер (Q=1,

Совершенно аналогично сигнал «1», поданный на вход K, установит триггер в состояние «0».

Таким образом, в триггере данного типа изменение выходного сигнала происходит только в моменты, когда потенциал «C» переходит из «1» в «0». Поэтому говорят, что эти триггеры тактируются срезом (или фронтом) в отличие от триггеров, тактируемых потенциалом.

Условное графическое обозначение триггера приведено на рисунке 51,в.

Если соединить вместе входы J и K, то JK-триггер превратится в Т-триггер. Пусть триггер находится в исходном состоянии (

5.1.5 Несимметричные триггеры

Несимметричный триггер (триггер Шмита) имеет два устойчивых состояния, однако, в отличие от симметричного триггера, нахождение его в том или ином устойчивом состоянии зависит от величины входного сигнала.

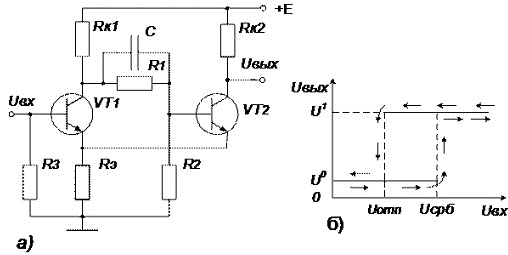

Несимметричный триггер на дискретных элементах состоит из двух транзисторов, в эмиттерную цепь которых включён резистор RЭ (Рисунок 52). При таком включении напряжение на базе транзистора VT1 зависит от значения коллекторного тока IК2 транзистора VT2. В свою очередь, базовая цепь VT2 через делитель R1/R2 соединена с коллекторной цепью транзистора VT1. Эти цепи создают замкнутую петлю положительной обратной связи, которая, как и в симметричном триггере, обеспечивает быстрое переключение триггера Шмита из одного устойчивого состояния в другое, когда оба транзистора работают в активном режиме.

Рисунок 52 Триггер Шмита на транзисторах

В отсутствие входного напряжения (Uвх=0) триггер находится в устойчивом состоянии. При этом транзистор VT2 открыт и насыщен, так как на его базу через резисторы Rк1, R1 подаётся положительное напряжение, а транзистор VT1 закрыт. За счёт протекающего коллекторного тока IК2=E/(RК2+RЭ) на резисторе RЭ создаётся падение напряжения и на базе VT1 относительно эмиттера действует запирающее напряжение UБЭ1=–RЭIК2. В таком состоянии триггера напряжение на выходе UВЫХ=U 0 =RЭIК2+UКЭнас.

Если увеличивать входное напряжение, то пока Uвх UОТП, необходимо, чтобы RК1>RК2.

Конденсатор C1 на устойчивые состояния триггера влияния не оказывает. Он выполняет функцию форсирующего конденсатора во время во время включения и выключения транзистора VT2 и тем самым способствует сокращению времени переключения триггера из одного устойчивого состояния в другое.

Несимметричный триггер может быть реализован на логических элементах. Для этого достаточно включить последовательно чётное число элементов НЕ и выход этой цепочки соединить со входом цепью обратной связи, образуемой резисторами R1 и R2 (Рисунок 53,а).

Рисунок 53 Триггер Шмита на логических элементах

С ростом Uвх повышается напряжение Uвх1, но пока Uвх1 0 . Когда Uвх1=Uпор, происходит переключение логических элементов и на выходе возникает сигнал UВЫХ=U¹. В результате схема переходит в другое устойчивое состояние. Напряжение срабатывания можно определить из приведённого выше выражения (5.3), если принять Uвх1=Uпор, UВЫХ=U¹, Uвх=Uсрб:

Естественно, что при Uвх1>Uсрб на выходе схемы сохраняется состояние лог. «1».

При уменьшении Uвх триггер переходит в исходное состояние, когда Uвх=Uотп. Значение Uотп определяется из соотношения (5.3), если положить Uвх1=Uпор, Uвых=U 1 , Uвх=Uотп.

Из соотношений (5.4) и (5.5) следует, что Uсрб>Uотп и, таким образом, амплитудная передаточная характеристика несимметричного триггера на ЛЭ имеет петлю гистерезиса. Вычитая (5.5) из (5.4), получаем

Откуда видно, ширина петли гистерезиса пропорциональна логическому перепаду ∆UЛ.

Несимметричные триггеры применяют в качестве формирователей импульсов прямоугольной формы при воздействии на вход, например, синусоидального напряжения (Рисунок 53,б).

Поскольку выходное напряжение резко возрастает при UВХ=UСРБ, то такие триггеры используют и в качестве компаратора напряжения — устройства, которое позволяет зафиксировать момент достижения сигналом некоторого заданного уровня.

Регистры — это функциональные узлы на основе триггеров, предназначенные для приёма, кратковременного хранения (на один или несколько циклов работы данного устройства), передачи и преобразования многоразрядной цифровой информации.

В зависимости от способа записи информации (кода числа) различают параллельные, последовательные и параллельно — последовательные регистры.

5.2.1 Параллельные регистры (регистры памяти)

Запись кода в параллельные регистры осуществляется параллельным кодом, то есть во все разряды регистра одновременно. Их функция сводится только к приёму, хранению и передаче информации. В связи с этим параллельные регистры называют регистрами памяти.

Параллельный N-разрядный состоит из N триггеров, объединённых общими цепями управления.

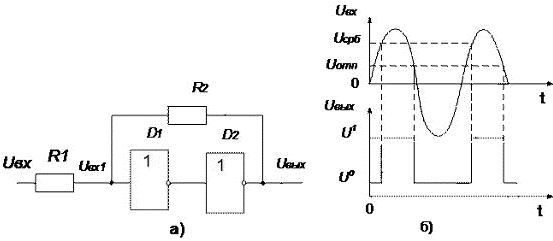

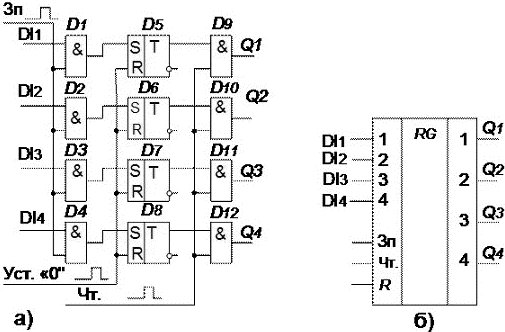

В качестве примера на рисунке 54,а приведена схема 4-разрядного параллельного регистра, построенного на RS-триггерах D5…D8. Элементы D1…D4 образуют цепь управления записью, а элементы D9…D12 — цепь управления чтением.

Рисунок 54 Функциональная схема а) и УГО б) параллельного регистра.

Перед записью информации все триггеры регистра устанавливают в состояние «0» путём подачи импульса «1» на их R-входы.

Записываемая информация подаётся на входы DI1…DI4. Для записи информации подаётся импульс «Зп», открывающий входные элементы «И». Код входного числа записывается в регистр. По окончании импульса «Зп» элементы D1…D4 закрываются, а информация, записанная в регистр, сохраняется несмотря на то, что входная информация может изменяться.

Для считывания информации подают сигнал «1» на вход «Чт». По этому сигналу на выходные шины регистра на время действия сигнала передаётся код числа, записанный в регистр. По окончанию операции чтения выходные ключи закрываются, а информация, записанная в регистр, сохраняется. То есть возможно многократное считывание информации. Условное графическое обозначение параллельного регистра приведено на рисунке 54,б.

5.2.2 Регистры сдвига

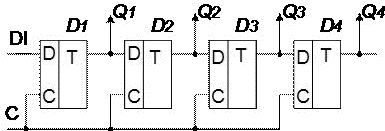

Регистры сдвига представляют собой цепочку последовательно включённых D-триггеров или RS- и JK-триггеров, включённых в режим D-триггера. Появление импульса на тактовом входе регистра сдвига вызывает перемещение записанной в нём информации на один разряд вправо или влево. Как и другие регистры, регистры сдвига используются для записи, хранения и выдачи информации, но основным их назначением является преобразование последовательного кода в параллельный или параллельного в последовательный.

Схема 4-разрядного регистра сдвига приведена на рисунке 55. Схема работает следующим образом. Благодаря тому, что выход предыдущего разряда соединён со входом «D» последующего, каждый тактовый импульс устанавливает последующий триггер в состояние, в котором до этого находился предыдущий. Так осуществляется сдвиг информации вправо.

Рисунок 54 4-разрядный регистр сдвига

Вход «D» первого триггера служит для приёма в регистр входной информации DI в виде последовательного кода. С каждым тактовым импульсом на этот вход должен подаваться код нового разряда входной информации.

Запись параллельного кода информации может быть произведена через нетактируемые установочные входы

С выхода «Q4» последнего триггера снимается последовательный выходной код. Код на этом выходе регистра появляется с задержкой относительно входного последовательного кода на число периодов тактовых импульсов, равное числу разрядов регистра.

Параллельный выходной код можно снять с выходов Q1…Q4 всех триггеров регистра сдвига, снабдив их выходными ключами, подобными выходным ключам параллельного регистра (См. рисунок 54,а).

5.2.3 Реверсивные регистры сдвига

Реверсивные регистры сдвига обеспечивают возможность сдвига информации как вправо, так и влево. Они имеют специальный вход управления направлением сдвига.

Поскольку транзисторы и логические элементы способны передавать сигналы только в одном направлении с входа на выход (слева направо), то, для сдвига информации влево, необходимо информацию с выхода последующих триггеров по специально созданным цепям подавать на входы предыдущих триггеров и записывать их следующим тактовым сигналом. Это эквивалентно сдвигу информации влево.

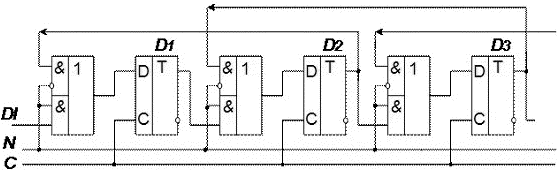

Фрагмент функциональной схемы реверсивного регистра сдвига приведён на рисунке 56.

Рисунок 56 Реверсивный регистр сдвига

Если сигнал на входе направления сдвига N=1, то потенциал на входе «Di» триггера определяется выходом Q триггера, стоящего слева от него. Если N=0, то выходом триггера, стоящего справа.

Таким образом, при N=1 тактовые импульсы производят сдвиг информации вправо, а при N=0 –— сдвиг информации влево.

5.2.4. Интегральные микросхемы регистров (примеры)

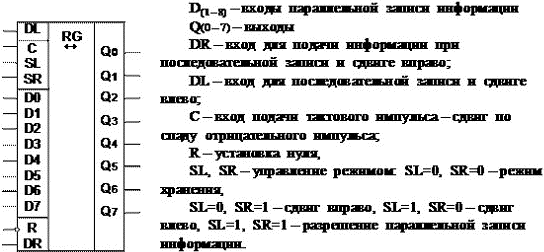

Интегральные микросхемы регистров, как и другие микросхемы, имеют дополнительные управляющие входы, расширяющие их функциональные возможности и делающие их универсальными. В качестве примера рассмотрим микросхему К155ИР13.

К155ИР13 — это 8-разрядный реверсивный регистр сдвига с возможностью параллельной записи информации. УГО этого регистра приведено на рисунке 57. Изучив назначение входных и выходных сигналов, легко усвоить функциональные возможности микросхемы и особенности её применения.

Рисунок 57 Реверсивный регистр сдвига и записи информации К155ИР13

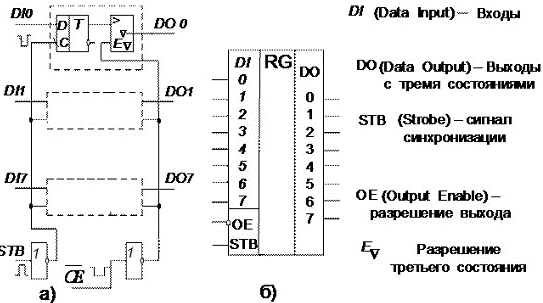

Буферный регистр КР580ИР82, входящий в состав МП-комплекта КР580, построен на D-триггерах и предназначен для записи и сохранения 8-разрядных данных в течение заданного промежутка времени. Этот регистр называют также регистром-защёлкой. Например, в МП-системах на МР КР580 он используется сохранения в течение машинного цикла байта состояния, а на МП1810 — адреса, поступающего по мультиплексированной шине адреса-данных. Его функциональная схема и условное графическое обозначение приведены на рисунке 58,а,б.

Рисунок 58 Буферный регистр КР580ИР82:

а) — функциональная схема, б) — УГО

Регистр состоит из 8-и D-триггеров, тактируемых фронтом, и 8-и элементов с тремя выходными состояниями. Схема управления построена на двух элементах ИЛИ-НЕ.

Если на вход

Таким образом, микросхема может работать в трёх режимах:

—

—

—

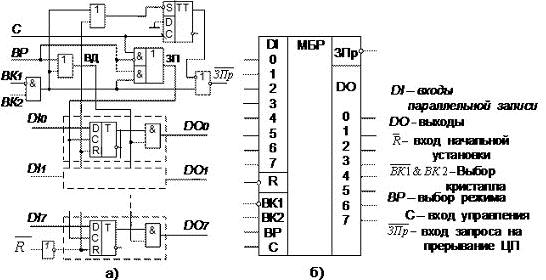

Многорежимный буферный регистр (МБР) К589ИР12 является универсальным 8-и разрядным регистром, состоящим из D-триггеров и выходных буферных схем с 3-мя устойчивыми состояниями. МБР имеет также встроенную селективную логику: «Схема управления режимами» и отдельный D-триггер для формирования запроса на прерывание центрального процессора.

МБР предназначен для использования в качестве портов ввода информации в МП от внешних устройств, или портов вывода информации из МП во внешние устройства.

Функциональная схема МБР и его УГО приведены на рисунке 59,а,б.

Рисунок 59 МБР К589ИР12: а) Функциональная схема, б) УГО.

Схема управления режимами (D1, D2, D4) в зависимости от сочетания управляющих сигналов C, ВР,

— Запись входной информации от внешнего устройства по сигналам

— Хранение информации по сигналам

— Выдачу информации по сигналам

— Передачу входной информации на выход (режим шинного формирователя) по сигналам

Схема управления прерываниями (D3, D5, D6) формирует запрос на прерывание для МП по окончании сигнала записи информации в МБР от внешнего устройства по спаду сигнала «C». Сброс сигнала

5.3 Счётчики импульсов

5.3.1 Требования, предъявляемые к счётчикам

В устройствах цифровой обработки информации измеряемый параметр (угол поворота, скорость, давление и т. п.) преобразуются в импульсы напряжения, число которых в соответствующем масштабе характеризует значение данного параметра. Эти импульсы подсчитываются счётчиками импульсов и выражаются в виде цифр.

Основными показателями счётчиков являются ёмкость и быстродействие.

Ёмкость, численно равная КСЧ, характеризует число импульсов, доступное счёту за один цикл. Как уже было показано выше, ёмкость определяется количеством разрядов счётчика.

Быстродействие или максимально возможная скорость работы оценивается двумя параметрами:

– Разрешающая способность tраз.сч — минимальное время между двумя входными сигналами, в течение которого ещё не возникают сбои в работе счётчика. Величина, обратная разрешающей способности, называется максимальной частотой счёта fmax. fmax определяет количество импульсов, которое может подсчитать счётчик за 1 сек.

– Время установки кода счётчика tуст — это время между моментом прихода входного сигнала и переходом счётчика в новое устойчивое состояние.

Для удовлетворения потребностей разработчиков цифровых электронных устройств различного назначения разработаны интегральные микросхемы счётчиков с широким спектром параметров. Всё многообразие счётчиков можно классифицировать по следующим признакам.

1 По направлению счёта:

2 По коэффициенту счёта:

• С постоянным произвольным коэффициентом счёта,

• С переменным коэффициентом счёта.

3 По способу организации внутренних связей:

• С последовательным переносом,

• С параллельным переносом,

• С комбинированным переносом,

Классификационные признаки независимы и могут встречаться в разных сочетаниях. Например, суммирующие счётчики могут быть как с последовательным, так и с параллельным переносом и могут иметь двоичный или десятичный коэффициент счёта.

5.3.2 Суммирующие счётчики

Простейшим счётчиком является Т-триггер, считающий до 2-х, то есть осуществляющий счёт и хранение не более 2-х сигналов.

Счётчик, образованный цепочкой из n триггеров сможет подсчитать в двоичном коде 2 n импульсов. Число n определяет количество разрядов двоичного числа, которое может быть записано в счётчик. Число 2 n называется модулем или коэффициентом счёта:

Схема простейшего 4-х разрядного счётчика приведена на рисунке 60,а. Принцип работы счётчика проиллюстрирован временными диаграммами, приведёнными на рисунке 60,б.

Рисунок 60 Схема двоичного суммирующего счётчика а)

и временные диаграммы его работы б).

Первый разряд счётчика переключается с приходом каждого входного импульса, что соответствует алгоритму работы Т-триггера. На каждые два входных импульса Т-триггер формирует один выходной импульс.

Второй разряд переключается в состояние «1» после прихода каждого 2-го импульса.

Третий разряд — после прихода каждого 4-го импульса.

Четвёртый разряд — после прихода каждого 8-го импульса.

Таким образом, единичные значения сигналов на выходах триггеров регистра появляются с приходом 1, 2, 4, 8 импульсов, что соответствует весовым коэффициентам двоичного кода. Поэтому с выходов триггеров регистра можно прочитать параллельный двоичный код числа импульсов, поступивших на его вход. Например, после прихода 5 импульсов единичные значения установятся на выходах Q1 и Q3 (см. пунктирную линию на рисунке 60,б), что соответствует коду числа 5: 0101B. Аналогично, после прихода 13-и импульсов на выходах триггеров установится код 1101B.

Если число входных импульсов NВХ>KСЧ, то при NВХ=KСЧ происходит переполнение счётчика, после чего счётчик возвращается в нулевое состояние и повторяет цикл работы.

После каждого цикла счёта на выходе последнего триггера возникают перепады напряжения, то есть формируется один импульс. Это свойство определяет второе назначение счётчиков — деление числа входных импульсов.

Если входные сигналы периодичны и следуют с частотой fВХ, то частота fВЫХ:

В этом случае коэффициент счёта определяется как коэффициент деления и обозначается KДЕЛ.

У счётчика в режиме деления частоты используется сигнал только последнего триггера, а промежуточные состояния остальных триггеров не учитываются.

Всякий счётчик может быть использован как делитель частоты.

5.3.3 Вычитающие и реверсивные счётчики

Реверсивный счётчик может работать в качестве суммирующего и вычитающего.

Суммирующий счётчик, как было показано выше, получается при подсоединении к входу последующего каскада прямого выхода предыдущего.

Каждый входной импульс увеличивает число, записанное в счётчик, на 1. Перенос информации из предыдущего разряда в последующий происходит при смене состояния предыдущего разряда (триггера) с 1 на 0.

Вычитающий счётчик получается при подсоединении к входу последующего каскада инверсного выхода предыдущего. Он действует обратным образом: двоичное число, хранящееся в счётчике, с каждым поступающим импульсом уменьшается на 1.

Перенос из младшего разряда в старший имеет место при смене состояния младшего разряда с 0 на 1.

Переполнение происходит после достижения счётчиком нулевого состояния, при этом в счётчик записывается максимально возможное значение, т.е. во все разряды — единицы.

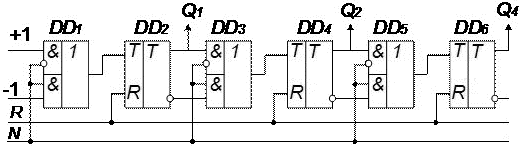

Путём включения в схему двоичного суммирующего счётчика (рисунок 60), дополнительных ЛЭ, переключающих на вход последующего триггера прямого и инверсного выходов предыдущего, получается схема реверсивного счётчика. Фрагмент схемы реверсивного счётчика приведён на рисунке 61.

Рисунок 61 Фрагмент схемы реверсивного счётчика

Схема имеет два входа для подачи входных сигналов: +1 — при работе в режиме суммирования, -1 — при работе в режиме вычитания. Дополнительный управляющий вход N задаёт направление счёта. При N=0 схема (рисунок 61) работает как суммирующий счётчик, а при N=1 — как вычитающий.

5.3.4 Счётчики с произвольным коэффициентом счёта

В двоичных счётчиках коэффициент счёта KСЧ=2 n и может быть равен 2, 4, 8, 16, 32 и т.д. На практике требуются счётчики с коэффициентом счёта не равным 2 n , например, 3, 6, 10, 12, 24 и др.

Они выполняются на основе двоичных счётчиков путём исключения у счётчиков с KСЧ=2 n соответствующего числа «избыточных» состояний S:

Например, двоично-десятичный (декадный) счётчик получают из 4-х разрядного, имеющего KСЧ=16, исключая 6 состояний.

Возможны 2 варианта построения схем:

а) Счёт циклически идёт от 0000 до 1001, а следующим импульсом обнуляется;

б) Исходным состоянием служит код 0110 числа 6 и счёт происходит до 11112=15, а следующим импульсом обнуляется.

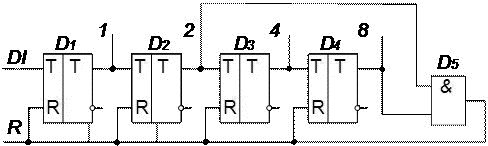

Рисунок 62 Схема счётчика с Ксч =10

Схема счётчика с KСЧ=10, реализованная по первому варианту, приведена на рисунке 62. По сравнению со схемой двоичного счётчика (Рисунок 60), имеющего KСЧ=24=16, в схему дополнительно введён элемент D5, обнуляющий счётчик при совпадении двух «1» с весовыми коэффициентами 2 и 8. Использование приведённой выше схемы и ЛЭ D5 с 4-мя входами, позволит получить счётчик с любым коэффициентом счёта от 2-х до 15-и.

Для реализации схемы по второму варианту используются триггеры, имеющие входы асинхронной установки триггера

5.3.5 Счётчики с последовательно-параллельным переносом

Все рассмотренные выше схемы счётчиков представляют собой счётчики с последовательным переносом. В этих счётчиках импульсы, подлежащие счёту, поступают на вход только одного первого триггера, а сигнал переноса передаётся последовательно от одного разряда к другому. Такие счётчики отличаются простотой схемы, но имеют невысокое быстродействие.

Счётчики с параллельным переносом строятся на синхронных триггерах.

Счётные импульсы подаются одновременно на тактовые входы всех триггеров, а каждый из триггеров цепочки служит по отношению к последующим только источником сигналов. Срабатывание триггеров параллельного счётчика происходит синхронно, и задержка переключения всего счётчика равна задержке для одного триггера. Следовательно, такие счётчики более быстродействующие. Их основным недостатком является большая мощность, потребляемая от источника входных сигналов, так как входные импульсы подаются на тактовые входы всех триггеров.

Для устранения недостатков рассмотренных выше счётчиков разработаны и используются счётчики с последовательно-параллельным переносом.

В счётчиках с последовательно-параллельным переносом триггеры объединены в группы так, что отдельные группы образуют счётчики с параллельным переносом, а группы соединяются с последовательным переносом. В роли групп могут быть и готовые счётчики.

Общий коэффициент счёта таких счётчиков равен произведению коэффициентов счёта всех групп.

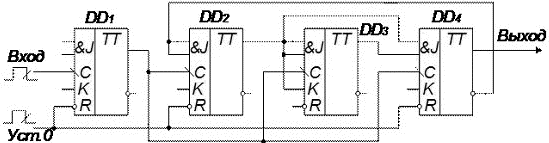

В качестве примера рассмотрим счётную декаду на JK-триггерах, приведённую на рисунке 63.

Рисунок 63 Счётная декада на JK-триггерах

Схема состоит из двух групп. Первая группа — это триггер DD1.

Вторая группа, состоящая из трёх триггеров DD2–DD4, представляет собой счётчик с параллельным переносом и тактируется выходным сигналом первого триггера. Группы соединены между собой последовательно.

Схема работает следующим образом.

При подаче на вход импульсов с 1-го по 8-ой декада работает как обычный двоичный счётчик импульсов.

К моменту прихода 8-го импульса на двух входах J 4-го триггера формируется уровень лог. «1». 8-ым импульсом этот триггер переключается в состояние лог. «1», а уровень лог. «0» с его инверсного выхода, подаваемый на вход «J» второго триггера, запрещает его переключение в единичное состояние под действием 10-го импульса.

10-ый импульс восстанавливает нулевое состояние 4-го триггера и цикл работы счётчика повторяется.

5.3.6 Универсальные счётчики в интегральном исполнении (Примеры)

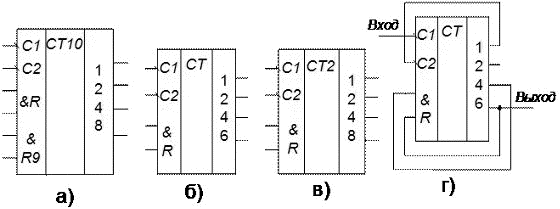

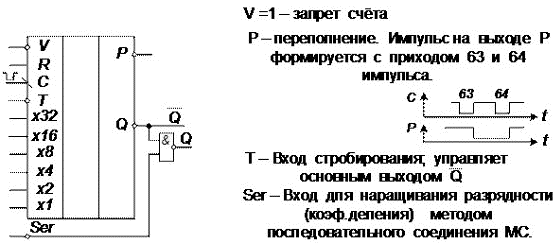

УГО которых приведены на рисунке 64 а, б, в представляют собой счётчики с последовательно-параллельным переносом, структурные схемы которых подобны схеме, приведённой на рисунке 63.

Рисунок 64 Микросхемы счётчиков К155ИЕ2, К155ИЕ4 и К155ИЕ5

Структурные схемы счётчиков содержат по 4-е JK-триггера в счётном режиме. Первый триггер имеет отдельный вход C1 и прямой выход — 1, три оставшиеся триггера соединены между собой так, что образуют параллельные счётчики с коэффициентами счёта равными 5 (К15ИЕ2), 6 (К155ИЕ4) и 8 (К1ИЕ5).

При соединении выхода первого триггера со входом C2 цепочки из 3-х триггеров образуются счётчики с коэффициентами счёта 10, 12 и 16 соответственно.

Микросхемы имеют по два входа R, объединённые по «И». Микросхема К155ИЕ2 имеет кроме того входы установки в состояние 9, при котором первый и последний разряды устанавливаются в «1», а остальные в «0», то есть 10012=9.

Наличие входов установки, например, в «0», позволяет строить делители частоты (счётчики) с различными коэффициентами деления (счёта) в пределах 2–16 без использования дополнительных логических элементов.

На рисунке 61,г показано преобразование счётчика, имеющего KСЧ=12, в десятичный.

До прихода 10-го импульса схема работает как делитель частоты на 12. Десятый импульс переводит триггеры МС в состояние, при котором на выходах 4 и 6 МС формируются лог. «1».

Эти уровни, поступая на входы R, объединённые по «И», переводят МС в состояние «0»; в результате чего KСЧ (KДЕЛ) становится равным 10.

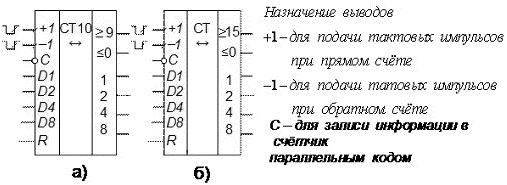

Реверсивные счётчики К155ИЕ6 и К155ИЕ7 (Рисунок 65)

Прямой счёт осуществляется при подаче отрицательных импульсов на вход +1, при этом на входах –1 и C должна быть лог. «1», а на входе R — лог. «0». Переключение триггеров происходит по спадам входных импульсов.

Рисунок 65 Реверсивные счётчики К155ИЕ6 а) и К15ИЕ7 б).

Уровни на выходах 1–2–4–8 соответствуют состоянию счёта в данный момент времени.

Отрицательный импульс на выходе ≥9 (≥15) формируется одновременно с 10 (или 16) импульсом на входе +1. Этот импульс может подаваться на вход +1 следующей МС многоразрядного счётчика. При обратном счёте входные импульсы подаются на вход –1, выходные импульсы снимаются с выхода ≤0.

Счётчик-делитель частоты с переменным коэффициентом деления К155ИЕ8 (Рисунок 66).

Микросхема содержит 6-разрядный двоичный счётчик, элементы совпадения и элемент собирания. Элементы совпадения блокируют прохождение импульсов, не совпадающих с запрограммированным кодом, а элемент собирания позволяет передавать на выход только выделенные импульсы.

Рисунок 66 Счётчик – делитель частоты К155ИЕ8

В результате средняя частота выходных импульсов может изменяться от 1/64 до 63/64 частоты входных импульсов.

Число импульсов на выходе

Источник