Способы адресации команд эвм

Исполнительный адрес — это номер ячейки памяти, к которой производится фактическое обращение.

В современных ЭВМ адресный код, как правило, не совпадает с исполнительным адресом.

Выбор способов адресации, формирования исполнительного адреса и преобразования адресов является одним из важнейших вопросов разработки ЭВМ. Рассмотрим способы адресации, используемые в современных ЭВМ :

1) Подразумеваемый операнд .

В команде может не содержаться явных указаний об операнде; в этом случае операнд подразумевается и фактически задается кодом операции команды.

2) Подразумеваемый адрес .

В команде может не содержаться явных указаний об адресе участвующего в операции операнда или адресе, по которому должен быть размещен результат операции, но этот адрес подразумевается.

3) Непосредственная адресация .

В команде содержится не адрес операнда, а непосредственно сам операнд. При непосредственной адресации не требуется обращения к памяти для выборки операнда и ячейки памяти для его хранения. Это способствует уменьшению времени выполнения программы и занимаемого ею объема памяти. Непосредственная адресация удобна для хранения различного рода констант.

4) Прямая адресация .

В адресной части команды может быть непосредственно указан исполнительный адрес.

5) Относительная (базовая) адресация .

При этом способе адресации исполнительный адрес определяется как сумма адресного кода команды и базового адреса, как правило хранящегося в специальном регистре — регистре базы .

Относительная адресация позволяет при меньшей длине адресного кода команды обеспечить доступ к любой ячейке памяти. Для этого число разрядов в базовом регистре выбирают таким, чтобы можно было адресовать любую ячейку оперативной памяти, а адресный код команды используют для представления лишь сравнительно короткого «смещения». Смещение определяет положение операнда относительно начала массива, задаваемого базовым адресом.

Лучший спонсор для вебмастеров ! Вы ещё не с нами ?!

6) Укороченная адресация .

Для уменьшения длины кода команды часто применяется так называемая укороченная адресация. Суть ее сводится к тому, что в команде задаются только младшие разряды адресов, а старшие разряды при этом подразумеваются нулевыми. Такая адресация позволяет использовать только небольшую часть фиксированных ячеек в начале всей адресуемой области памяти, и поэтому применяется лишь совместно с другими способами адресации.

Регистровая адресация является частным случаем укороченной, когда в качестве фиксированных ячеек с короткими адресами используются регистры (ячейки сверхоперативной или местной памяти) процессора. Например, если таких регистров 16, то для адреса достаточно четырех двоичных разрядов. Регистровая адресация наряду с сокращением длины адресов операндов позволяет увеличить скорость выполнения операций, так как уменьшается число обрашений к оперативной памяти.

7) Косвенная адресация .

Адресный код команды в этом случае указывает адрес ячейки памяти, в которой находится адрес операнда или команды. Косвенная адресация широко используется в малых и микроЭВМ, имеющих короткое машинное слово, для преодоления ограничений короткого формата команды (совместно используются регистровая и косвенная адресация).

8) Адресация слов переменной длины .

Эффективность вычислительных систем, предназначенных для обработки данных, повышается, если имеется возможность выполнять операции со словами переменной длины. В этом случае в машине может быть предусмотрена адресация слов переменной длины, которая обычно реализуется путем указания в команде местоположения в

памяти начала слова и его длины.

9) Стековая адресация .

Стековая память, реализующая безадресное задание операндов, особенно широко используется в микропроцессорах и миниЭВМ.

Стек представляет собой группу последовательно пронумерованных регистров или ячеек памяти, снабженных указателем стека, в котором автоматически при записи и считывании устанавливается номер (адрес) последней занятой ячейки стека (вершины стека). При операции записи заносимое в стек слово помещается в следующую по порядку свободную ячейку стека, а при считывании из стека извлекается последнее поступившее в него слово.

10) Автоинкрементная и автодекрементная адресации .

Поскольку регистровая косвенная адресация требует предварительной загрузки регистра косвенным адресом из оперативной памяти, что связано с потерей времени, такой тип адресации особенно эффективен при обработке массива данных, если имеется механизм автоматического приращения или уменьшения содержимого регистра при каждом обращении к нему. Такой механизм называется соответственно автоинкрементной и автодекрементной адресацией. В этом случае достаточно один раз загрузить в регистр адрес первого обрабатываемого элемента массива, а затем при каждом обращении к регистру в нем будет формироваться адрес следующего элемента массива.

При автоинкрементной адресации сначала содержимое регистра используется как адрес операнда, а затем получает приращение, равное числу байт в элементе массива. При автодекрементной адресации сначала содержимое указанного в команде регистра уменьшается на число байт в элементе массива, а затем используется как адрес операнда.

Автоинкрементная и автодекрементная адресации могут рассматриваться как упращенный вариант индексации — весьма важного механизма преобразования адресных частей команд и организации вычислительных циклов, поэтому их часто называют автоиндексацией.

Для реализуемых на ЭВМ методов решения математических задач и обработки данных характерна цикличность вычислительных процессов, когда одни и те же процедуры выполняются над различными операндами, упорядоченно расположенными в памяти. Поскольку операнды, обрабатываемые при повторениях цикла, имеют разные адреса, без использования индексации требовалось бы для каждого повторения составлять свою последовательность команд, отличающихся адресными частями.

Программирование циклов существенно упрощается, если после каждого выполнения цикла обеспечено автоматическое изменение в соответствующих командах их адресных частей согласно расположению в памяти обрабатываемых операндов. Такой процесс называется модификацией команд, и основан на возможности выполнения над кодами команд арифметических и логических операций.

Управление вычислительным циклом должно обеспечивать повторение цикла нужное число раз, а затем выход из него.

Автоматическая модификация команд и управление вычислительными циклами в современных ЭВМ обеспечиваются механизмом индексации. Это понятие включает в себя специальный способ кодирования команд, командные и аппаратурные средства задания и выполнения модификации команд и управления вычислительными циклами. Упомянутые средства часто называют индексной арифметикой.

Для выполнения индексации в машину вводятся так называемые индексные регистры. Исполнительный адрес при индексации формируется путем сложения адресного кода команды (смещения) с содержимым индексного регистра (индексом), а при наличии базирования — и с базовым адресом.

Для управления индексацией используются команды, задающие операции над содержимым индексных регистров — команды индексной арифметики. Можно отметить основные виды индексных операций:

— засылка в соответствующий индексный регистр начального значения индекса;

— проверка окончания циклических вычислений.

Источник

Система кодирования команд. Способы адресации

Система кодирования команд

Запись любой команды определяется ее форматом. Формат команды – это структура команды, позволяющая распознать назначение отдельных ее полей.

Исходя из определения, команда должна содержать информацию о выполняемой операции , адресах операндов и адресе ячейки ЗУ для записи результата. Этому в наибольшей степени соответствует формат команды , содержащий поле кода операции и три адресных поля. Такая система кодирования команд называется трехадресной (рис.11.1,в).

Схема выполнения трехадресной команды имеет вид:

Здесь (А1) и (А2) – адреса ячеек ЗУ, в которых хранятся первый и второй операнды соответственно; * – знак обобщенной операции (например, сложение или умножение ), задаваемой полем кода операции (КОп). Знак » -> » обозначает передачу результата операции в ячейку памяти с адресом А3 .

Для выполнения операции сложения операндов, находящихся по адресам a и b , с записью результата в ячейку c ( c = a + b ) требуется одна команда такого формата:

Здесь ADD – код операции сложения.

Формат двухадресной команды представлен на рис.11.1,б. Выполнение операции с помощью такой команды проходит по следующей схеме:

Выполнение того же самого действия c = a + b в двухадресной системе кодирования команд потребует уже двух команд, например:

| КОп | А1 | А2 | |

| ADD | a | b | a = a + b |

| MOV | c | a | c = a |

Одноадресная команда имеет формат, приведенный на рис.11.1,а. Обычно ЭВМ с одноадресной системой команд имеют особую структуру, в состав которой входит специальный регистр ( регистр результата – РР ). Он служит для хранения результата операции и используется в качестве одного из операндов при выполнении операции ( рис. 11.2).

Схема выполнения операции на ЭВМ с одноадресной системой команд имеет вид:

Операцию c = a + b в одноадресной системе команд можно выполнить следующим образом:

| КОп | А1 | |

| MOVR | a | РР = a |

| ADD | b | РР = РР + b |

| MOVS | c | c = РР |

Рассмотренные форматы команд используются при так называемом естественном порядке выполнения программы. При этом подразумевается, что после выполнения любой команды, не меняющей в явном виде порядок выполнения программы, очередная команда выбирается из ячейки ЗУ, располагающейся сразу же вслед за ячейкой (или ячейками), содержащей код текущей команды. При четырехадресной системе кодирования команд (рис.11.1,г) первые три адреса выполняют те же функции, что и в трехадресной команде, а четвертый адрес указывает адрес ячейки, где хранится следующая выполняемая команда . Такая система обеспечивает принудительный порядок выполнения команд программы. Она хотя и повышает гибкость программирования, но практического применения не получила. Основной причиной этого является существенное увеличение размера каждой команды и, соответственно, увеличение объема ЗУ, необходимого для размещения программы, в то время как реальной потребности в такой кодировке каждой команды не существует.

Несколько особое положение занимает безадресное кодирование команд . Оно используются в компьютерах, имеющих стековую организацию памяти . Обращение к ячейкам такой памяти производится последовательно с помощью специального указателя стека ( УС ), определяющего рабочую в данный момент ячейку. Каждая ячейка снабжена тэгом – специальным признаком хранимой информации. Такая ЭВМ имеет структуру, представленную на рис. 11.3. В ее состав помимо АЛУ входят два специальных буферных регистра РР1 и РР2 . Здесь значение тэгов следующее: Op – в данной ячейке хранится операнд , C – признак наличия в ячейке кода операции .

Проиллюстрируем работу такой ЭВМ на примере вычисления выражения ((a + b) * c — d) / e .

На первых двух тактах работы из памяти извлекаются операнды a и b и помещаются в рабочие регистры РР1 и РР2 . Считав следующую ячейку стековой памяти, устройство управления по ее тэгу определяет, что данная информация представляет собой код операции . Этот код направляется в АЛУ , где и проводится сложение хранящихся в регистрах операндов с записью результата в один из рабочих регистров. Так как в следующей ячейке хранится операнд , то он направляется в РР , свободный от записанного результата. После этого производится выполнение следующей операции и так далее.

Такая структура ЭВМ обеспечивает высокое быстродействие , но требует весьма сложного программирования.

Взаимозависимость формата команды и основных параметров ЭВМ

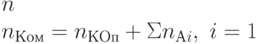

Важной характеристикой команды служит ее длина, которая складывается из длины поля кода операции и суммы длин адресных полей:

где n – количество адресных полей в команде.

Максимальное количество операций, которое может быть закодировано в поле кода операций длиной nкоп, составляет

Тогда по известному количеству команд ( K ), составляющих систему команд данной ЭВМ, можно определить необходимую длину поля операции:

Естественно, что эта величина должна быть минимально возможным целым числом. Так, для ЭВМ, имеющей систему команд из 100 команд, длина поля кода операции составит 7 бит.

Если поле адреса команды содержит просто номер ячейки ЗУ, к которой производится обращение, то длина этого поля определяется следующим образом:

где VЗУ – объем запоминающего устройства.

Правомерна и другая постановка задачи – определение максимального объема запоминающего устройства ( VЗУmax ), к которому можно обратиться при заданной длине поля адреса. В этом случае

Современные ЭВМ имеют, как правило, запоминающие устройства с минимальной адресуемой единицей 1 байт ( 1 байт = 8 бит ). Поэтому, например, адресация ЗУ объемом 1 мегабайт ( 1М байт = 2 20 байт ) требует 20 разрядов адресного поля, а поле адреса длиной 16 разрядов позволяет обращаться к памяти максимального объема 64 килобайта ( 1К байт = 2 10 байт ).

Одним из способов уменьшения длины поля адреса является введение в состав ЭВМ дополнительно специального блока памяти небольшого объема – регистровой памяти ( РП ). Это запоминающее устройство имеет высокое быстродействие и служит для хранения часто используемой информации: промежуточных результатов вычислений, счетчиков циклов, составляющих адреса при некоторых режимах адресации и т.д.. Так как объем РП невелик, адресация ее элементов требует относительно короткого адресного поля. Например, для регистровой памяти объемом 8 регистров требуется всего лишь трехразрядное адресное поле.

Источник