- Наращивание (каскадирование) дешифраторов

- Комбинационные микросхемы. Часть 1

- 17.3. Наращивание размерности дешифратора

- 17.4. Воспроизведение произвольных логических функций с помощью дешифратора

- 17.5. Мультиплексор

- Критерии взаимодействия ИМС в устройствах(эл аспект)

- Главная > Документ

- Билет1

- Билет2

- Билет3

- Дешифраторы/демультиплексоры

- Билет4

- Таблица 2.9

- Билет5

Наращивание (каскадирование) дешифраторов

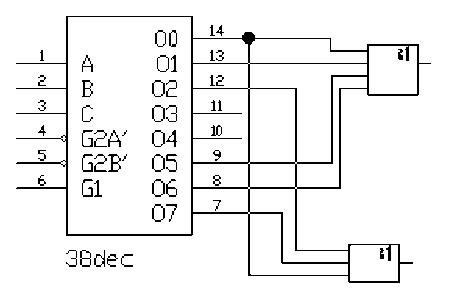

ИМС дешифраторов имеют ограниченное число адресных входов и информационных выходов. Увеличение их возможно путем наращивания (каскадирования), которое можно осуществлять двумя способами: объединением нескольких дешифраторов в пирамидальную схему (рис. 1.3), или последовательным соединением разрешающих входов через внешние логические элементы или непосредственно друг с другом (рис. 1.3 и 1.4).

При наращивании дешифраторов разряды двоичного адресного кода разделяются на старшие (СРА) и младшие (МРА) разряды адреса (табл. 1.3). СРА с помощью дешифратора DD1 (рис. 1.3) или входов стробирования (рис. 1.4) разрешают функционирование одного из основных дешифраторов DD2…DD9 (рис. 1.3) или дешифраторов DD1… DD4 (рис. 1.4).

МРА подаются параллельно на адресные входы всех выходных дешифраторов. Однако активируется только один соответствующий выход выбранного СРА дешифратора.

Рис.1.3. Пирамидальная схема наращивания дешифратора 6→64

Рис. 1.4. Дешифратор 5→32 на базе ИМС К555 ИД7 (на вход Е1

схемы ДД1 постоянно подан сигнал лог. “1”)

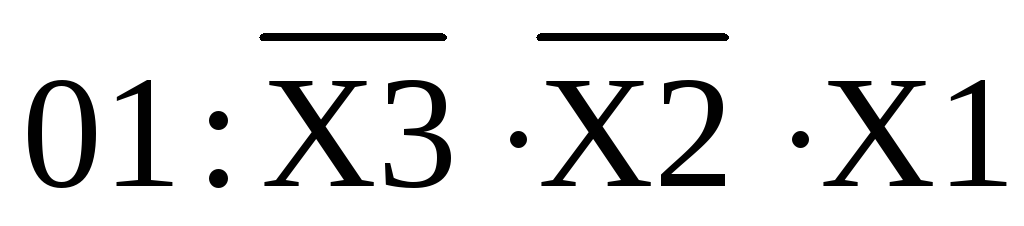

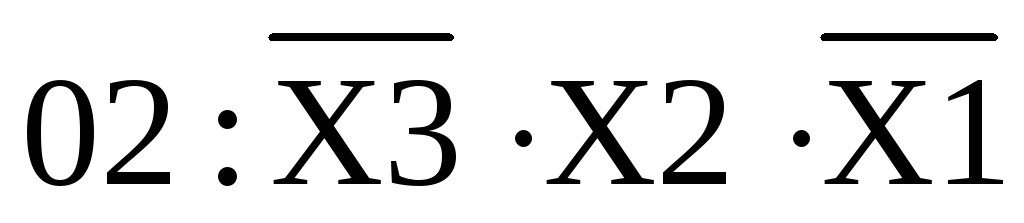

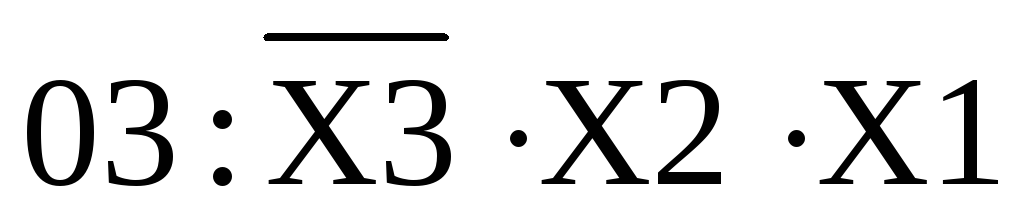

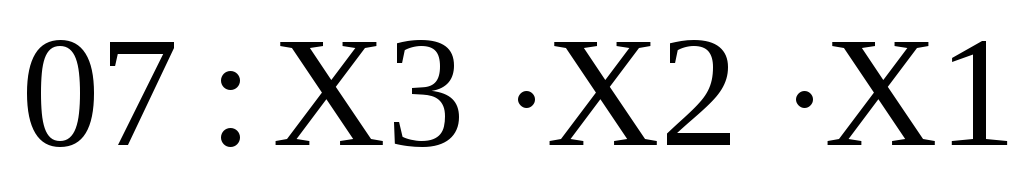

Например, при наличии на адресных входах двоичного кода

0110002 СРА разрешают функционирование (выбирают) ИМС DD5 (рис.1.3) и DD4 (рис. 1.4), а МРА активизируют вход 24 этих схем.

На рис. 1.3 и 1.4 показано, как увеличение числа входов разрешения расширяет возможности схем. Наличие одного входа разрешения требует дополнительной ИМС дешифратора DD1 на

рис.1.3. Наличие, например, трех входов разрешения, как у ИМС

555ИД7 (см. рис. 1.4), позволяет на трех таких ИМС без дополнительных элементов построить дешифратор 5→24, а на четырех ИМС 555ИД7 и одном инверторе – дешифратор 5→32.

На восьми ИМС 555ИД7 и двух инверторах – дешифратор

6→64 на ИМС 155ИД3, имеющих два входа разрешения с активным

= E1 = 0 ). Для построения дешифратора 5→32 требуется

две схемы 155ИД3 и один инвертор, а дешифратора 6→64 – четыре

ИМС 155ИД3 и два инвертора.

При изучении вопросов каскадирования следует обратить внимание на ИМС К555ИД4, структура которой (см. рис. 1.2) позволяет использовать её в различных вариантах. Два дешифратора этой схемы можно включить различными способами и получить, например, дешифратор 3→8 со входом стробирования (рис. 1.5,а) и дешифратор 4→10 (рис. 1.5,б). Приняв за основу схему (см. рис. 1.5,а), на ИМС К55ИД4 можно построить дешифратор

4→16 по схеме, аналогичной рис.1.4, а приняв за основу пирамидальную схему (см. рис. 1.3), – дешифратор 6→64. Эта ИМС может быть использована также в качестве демультиплексора, что будет рассмотрено ниже, в разделе 3.3, данного учебного пособия.

При наращивании дешифраторов, не имеющих входов разрешения, например дешифратора 4→10 (155ИД1, 555ТИД10,

564ИД1), можно использовать для стробирования старший разряд адресных входов (A4).

Рис.1.5. Дешифраторы на базе ИМС К555 ИД4: а 3→8; б 4→10

Материал взят из книги Цифровые интегральные микросхемы (Асмолов Г.И.)

Источник

Комбинационные микросхемы. Часть 1

Наиболее типичное применение дешифраторов состоит именно в дешифрировании входных кодов, при этом входы С используются как стробирующие, управляющие сигналы. Номер активного (то есть нулевого) выходного сигнала показывает, какой входной код поступил. Если нужно дешифровать код с большим числом разрядов, то можно объединить несколько микросхем дешифраторов (пример показан на рис. 5.3).

При этом старшие разряды кода подаются на основной дешифратор , выходы которого разрешают работу нескольких дополнительных дешифраторов . На объединенные входы этих дополнительных дешифраторов подаются младшие разряды входного кода. Из пяти микросхем дешифраторов 2–4 можно получить дешифратор 4–16, как показано на рисунке (хотя лучше, конечно, взять готовую микросхему). Точно так же из девяти микросхем 3–8 можно получить дешифратор 6–64, а из семнадцати микросхем 4–16 — дешифратор 8–256. Еще одно распространенное применение дешифраторов — селекция (выбор) заданных входных кодов. Появление отрицательного сигнала на выбранном выходе дешифратора будет означать поступление на вход интересующего нас кода. В данном случае увеличивать число разрядов входного селектируемого кода гораздо проще, чем в предыдущем (см. рис. 5.3). Например, две микросхемы 4–16 позволяют селектировать 8-разрядный код (рис. 5.4). В примере на рисунке селектируется 16-ричный код 2А (двоичный код 0010 1010). При этом один дешифратор работа ет с младшими четырьмя разрядами кода, а другой — со старшими четырьмя разрядами. Объединяются дешифраторы так, что один из них разрешает работу другого по входам –С1 и –С2. Применяя механические переключатели выходов дешифраторов (тумблеры, перемычки), можно легко изменять код, селектируемый данной схемой.

Еще одно важное применение дешифраторов состоит в перекоммутации одного входного сигнала на несколько выходов. Или, другими словами, дешифратор в данном случае выступает в качестве демультиплексора входных сигналов, который позволяет разделить входные сигналы, приходящие в разные моменты времени, на одну входную линию (мультиплексированные сигналы). При этом входы 1, 2, 4, 8 дешифратора используются в качестве управляющих, адресных, определяющих, на какой выход переслать пришедший в данный момент входной сигнал (рис. 5.5), а один из входов С выступает в роли входного сигнала, который пересылается на заданный выход. Если у микросхемы имеется несколько стробирующих входов С, то оставшиеся входы С можно использовать в качестве разрешающих работу дешифратора .

Как и для любых других цифровых микросхем, для дешифраторов наиболее критична ситуация одновременного или почти одновременного изменения входных сигналов. Например, если стробы С постоянно разрешают работу дешифратора , то в момент изменения входного кода на любом выходе дешифратора могут появиться паразитные отрицательные короткие импульсы. Это может быть связано как с неодновременным выставлением разрядов кода (из-за несовершенства микросхем источников кода или из-за разных задержек распространения по линиям связи), так и с внутренними задержками самих микросхем дешифраторов .

Если такие паразитные импульсы нужно исключить, то можно применять синхронизацию с помощью стробирующих сигналов. Используемый для этого сигнал С должен начинаться после текущего изменения кода, а заканчиваться до следующего изменения кода, то есть должен быть реализован вложенный цикл . На рис. 5.6 показано, как будет выглядеть выходной сигнал дешифратора без стробирования и со стробированием.

На втором уровне представления (модель с временными задержками) также надо учитывать, что задержки дешифратора больше задержки простых логических элементов примерно вдвое для входного кода и примерно в полтора раза — для стробирующих входов. То есть если попытаться заменить дешифратор схемой на логических элементах, то такой дешифратор получится медленнее. Точные величины задержек надо смотреть в справочниках.

Дешифраторы , имеющие выходы типа ОК (ИД5, ИД10), удобно применять в схемах позиционной индикации на светодиодах. На рис. 5.7 приведен пример такой индикации на микросхеме ИД5, которая представляет собой два дешифратора 2–4 с объединенными входами для подачи кода и стробами, позволяющими легко строить дешифратор 3–8. При этом старший разряд кода выбирает один из дешифраторов 2–4 (нуль соответствует верхнему по схеме дешифратору, а единица — нижнему). То есть в данном случае номер горящего светодиода равен входному коду дешифратора . Такая индикация называется позиционной.

Выходы микросхем дешифраторов с ОК можно объединять между собой для реализации проводного ИЛИ (рис. 5.8). Нуль на объединенном выходе будет тогда, когда хотя бы на одном из выходов вырабатывается нуль. При равномерном пошаговом наращивании входного кода (например, с помощью счетчика) такое решение позволяет формировать довольно сложные последовательности выходных сигналов. Правда, каждый выход дешифратора может использоваться для получения только одного выходного сигнала. Это ограничивает возможности таких схем.

Шифраторы используются гораздо реже, чем дешифраторы . Это связано с более специфической областью их применения. Значительно меньше и выбор микросхем шифраторов в стандартных сериях. В отечественных сериях шифраторы имеют в названии буквы ИВ.

Источник

17.3. Наращивание размерности дешифратора

Из малоразрядных дешифраторов можно построить схему, эквивалентную схеме дешифратора большей разрядности. Для этого входные слова делятся на поля. Разрядность поля младших разрядов соответствует числу входов имеющегося дешифратора. Оставшиеся поля старших разрядов служат для получения сигналов разрешения работы одного из дешифраторов, декодирующих поле младших разрядов. Работу схемы рассмотрим на примере числа 11001. Это число 25 в десятичной системе счисления. На входе дешифратора первого яруса имеется код 11, его выход №3, что разрешает работу четвертого дешифратора 2 яруса. На входе дешифратора №4 действует код 001, поэтому единица появится на его первом выходе, т. е. на 25-том выходе всей схемы.

Рис. 19. Наращивание размерности дешифратора

Разрешение работы дешифратора осуществляется подачей «1» на разрешающий вход дешифратора первого яруса.

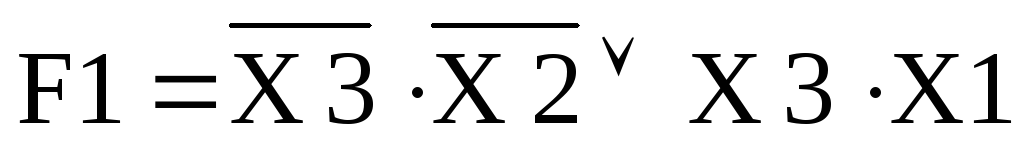

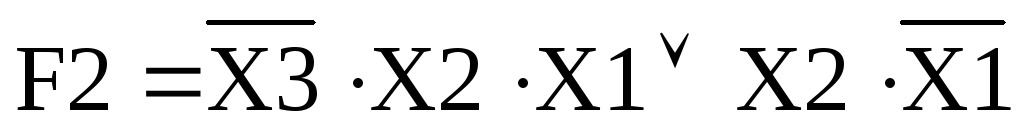

17.4. Воспроизведение произвольных логических функций с помощью дешифратора

Дешифраторы со схемами ИЛИ можно использовать для воспроизведения произвольных логических функций. На выходах дешифратора вырабатываются все конъюнктивные термы, которые только можно составить из данного числа аргументов. Логическая функция в СДНФ есть дизъюнкция некоторого числа таких термов. Собирая нужные термы по схеме ИЛИ, можно получить любую функцию данного числа аргументов.

Разберём пример следующего соединения:

Рис. 20. Пример соединения дешифратора и логических вентилей ИЛИ для получения произвольных логических функций

Подобное решение может быть целесообразно при необходимости выработки нескольких функций одних и тех же переменных.

17.5. Мультиплексор

Мультиплексор — это функциональный узел, который осуществляет управляемую коммутацию информации, поступающей по N параллельным каналам, на одну выходную линию. Коммутация есть последовательный опрос и передача информации. Коммутация определённой входной линии происходит в соответствии с двоичным адресным кодом An-1An. A1A0. Входы А0..Аn-1 являются адресными. Их значение определяет одну из переменных Х;, передаваемых на выход F. Если адресный код имеет n-разрядов, то можно осуществить N=2 n комбинаций адресных сигналов, каждый из которых обеспечивает коммутацию информации, поступающей по одному из N входов на выход. В простейшем случае двухразрядового адресного кода n=2 и максимальное число входных линий N=4. Таблица истинности такого мультиплексора 4-1 (Mux 4-1) выглядит следующим образом:

Источник

Критерии взаимодействия ИМС в устройствах(эл аспект)

Главная > Документ

| Информация о документе | |

| Дата добавления: | |

| Размер: | |

| Доступные форматы для скачивания: |

Билет1

Критерии взаимодействия ИМС в устройствах(эл аспект).Практич вопр эл сопр.

Билет2

Мультиплесоры: хар-ка ИМС стандартн серий,УГО, наращивание размерн, основные парам.

Мультиплексоры осуществляют подключение одного из входных каналов к выходному под управлением управляющего (адресующего) слова. Разрядности каналов могут быть различными, мультиплексоры для коммутации многоразрядных слов составляются из одноразрядных.

Рис. 2.9. Упрощенное представление мультиплексора многопозиционным ключом (а) и реализация мультиплексора на элементах И-НЕ (б)

Входы мультиплексора делятся на две группы: информационные и адресующие. Работу мультиплексора можно упрощенно представить с помощью многопозиционного ключа. Для одноразрядного мультиплексора это представлено на рис. 2.9, а. Адресующий код А задает переключателю определенное положение, соединяя с выходом F один из информационных входов х i . При нулевом адресующем коде переключатель занимает верхнее положение х о , с увеличением кода на единицу переходит в соседнее положение х i и т. д.

Работа мультиплексора описывается соотношением

которое иногда называется мультиплексной формулой. При любом значении адресующего кода все слагаемые, кроме одного, равны нулю. Ненулевое слагаемое равно х i , где i — значение текущего адресного кода.

Схемотехнически мультиплексор реализует электронную версию показанного переключателя, имея, в отличие от него, только одностороннюю передачу данных. На рис. 2.9, б показан мультиплексор с четырьмя информационными входами, двумя адресными входами и входом разрешения работы. При отсутствии разрешения работы (Е = 0) выход F становится нулевым независимо от информационных и адресных сигналов.

В стандартных сериях размерность мультиплексоров не более 16х1.

Наращивание размерности мультиплексоров возможно с помощью пирамидальной структуры из нескольких мультиплексоров. При этом первый ярус схемы представляет собою столбец, содержащий столько мультиплексоров, сколько необходимо для получения нужного числа информационных входов. Все мультиплексоры столбца адресуются одним и тем же кодом, составленным из соответствующего числа младших разрядов общего адресного кода (если число информационных входов схемы равно 2 n , то общее число адресных разрядов равно n, младшее поле n 1 адресного кода используется для адресации мультиплексоров первого яруса). Старшие разряды адресного кода, число которых равно п — n 1 , используются во втором ярусе, мультиплексор которого обеспечивает поочередную работу мультиплексоров первого яруса на общий выходной канал.

Пирамидальная схема, выполняющая функции мультиплексора «32-1» и построенная на мультиплексорах меньшей размерности, показана на рис. 2.10 (сокращение MUX от английского Multiplexer).

Билет3

Дешифраторы/демультиплексоры

Дешифраторы относятся к преобразователям кодов. Двоичные дешифраторы преобразуют двоичный код в код «1 из N». В кодовой комбинации этого кода только одна позиция занята единицей, а все остальные — нулевые.

Доичный дешифратор, имеющие n входов должен иметь 2 n выходов, соответствующих числу разных; комбинаций в.n-разрядном двоичном коде.

В зависимости от входного двоичного кода на выходе дешифратора возбуждается одна и только одна из выходных цепей.

Если часть входных наборов не используется, то дешифратор называют неполным, и у него число выходов меньше 2 n .

Рис. 2.4. Условное обозначение (а) и схемная реализация (б) двоичного дешифратора

В условном обозначении дешифраторов проставляются буквы DC (от английского Decoder): Входы дешифратора принято обозначать их двоичными весами. Кроме информационных входов дешифратор обычно имеет один или более входов, разрешения работы обозначаемых как EN (Enable). При наличии разрешения по этому входу дешифратор работает описанным выше образом, при его отсутствии все выходы дешифратора пассивны. Если входов разрешения несколько, то сигнал разрешения работы образуется как конъюнкция сигналов отдельных входов. Условное графическое обозначение полного двоичного дешифратора показано на рис. 2.4, а. Часто дешифратор имеет инверсные выходы. В этом случае только один выход имеет нулевое значение, а все остальные единичное. При запрещении работы дешифратора на всех его выходах будет присутствовать логическая единица.

Функционирование дешифратора описывается системой конъюнкций:

Схемотехническая реализация дешифраторов

Схемотехнически дешифратор представляет собою совокупность конъюнкторов (или элементов И-НЕ в дешифраторах с инверсными выходами), не связанных между собой. Каждый коныонктор (или элемент И-НЕ) вырабатывает одну из выходных функций. Кроме элементов для выработки выходных функций, дешифратор, как и многие другие ИС, снабжен схемами для выработки парафазных сигналов из однофазных (прямых), поступающих на входы ИС. Заметим, что входная прямая переменяв» непосредственно в схеме не используется, а вырабатывается повторно как двойная инверсия от входной. Это сделано для того, чтобы максимально разгружать линии внешних входов (здесь внешние входы нагружены только на один вход инвертора).* Внешние линии входов максимально разгружаются всегда, поскольку они и без того нагружены емкостью из-за своей относительно большой длины и конструкции выводов корпуса ИС, что снижает скорость передачи сигнала по линии.

Сокращенная схема дешифратора с показом одной входной линии и одной выходной линии (для определенности взята линия с номером 5) дана на рис. 2.4, б.

Время установления выходного сигнала дешифратора

где tз.инв. — задержка сигнала в инверторе; t, 10 ,1з 01 — задержки переключений логического элемента.

Видно, что дешифратор относится к числу быстродействующих узлов.

Как известно, корпуса ИС с большим числом выводов изготовлять сложно, и они дороги. С этой точки зрения дешифраторы относятся к крайне неудачным схемам, т. к. у них при простой внутренней структуре и малом числе схемных элементов много внешних выводов. Для размещения в обычном недорогом корпусе годится только дешифратор с 4 информационными входами. Более «размерных» дешифраторов в сериях ИС нет.

Рис. 2.5. Схема наращивания размерности двоичного дешифратора

Наращивание размерности дешифратора

Малоразрядность стандартных дешифраторов ставит вопрос о наращивании их разрядности. Из малоразрядных дешифраторов можно построить схему, эквивалентную дешифратору большей разрядности. Для этого входное слово делится на поля. Разрядность поля младших разрядов соответствует числу входов имеющихся дешифраторов. Оставшееся поле старших разрядов служит для получения сигналов разрешения работы одного из дешифраторов, декодирующих поле младших разрядов.

В качестве примера на рис. 2.5 приведена схема дешифрации пятиразрядного двоичного кода с помощью дешифраторов «3-8» и «2-4»- Для получения нужных 32 выходов составляется столбец из четырех дешифраторов «3-8». Дешифратор «2-4» принимает два старших разряда входного кода. Возбужденный единичный выход этого дешифратора отпирает один из дешифраторов столбца по его входу разрешения. Выбранный дешифратор столбца расшифровывает три младших разряда входного слова.

Каждому входному слову, соответствует возбуждение только одного выхода. Например, при дешифрации слова Х 4 Х 3 Х 2 Х 1 X 0 = 11001 2 = 25 10 на входе дешифратора первого яруса имеется код 11, возбуждающий его выход номер три (показано крестиком), что разрешает работу DC4. На входе DC4 действует код 001, поэтому единица появится на его первом выходе, т. е. на 25 выходе схемы в целом, что и требуется.

Общее разрешение или запрещение работы схемы осуществляется по входу EN дешифратора первого яруса.

Рис. 2.6. Схема воспроизведения произвольных логических функций с помощью дешифратора. и дизъюнкторов

Дешифраторы совместно со схемами ИЛИ можно использовать для воспроизведения произвольных логических функций. Действительно, на выходах дешифратора вырабатываются все конъюнктивные термы (конституенты единицы), которые только можно составить из данного числа аргументов. Логическая функция в СНДФ есть дизъюнкция некоторого числа таких термов. Собирая нужные термы по схеме ИЛИ, можно получить любую функцию данного числа элементов.

На рис. 2,6 в качестве примера показана схема выработки двух функций

Демультиплексоры выполняют операцию, обратную операции мультиплексоров — передают данные из одного входного канала в один из нескольких каналов-приемников. Многоразрядные демультиплексоры составляются из нескольких одноразрядных. Условное обозначение демультиплексоров на примере размерности » 1 -4″ показано на рис. 2.11.

Нетрудно заметить, что дешифратор со входом разрешения работы будет работать в режиме демультиплексора, если на вход разрешения подавать информационный сигнал. Действительно, при единичном значении этого сигнала адресация дешифратора (подача адресного кода на его входы) приведет к возбуждению соответствующего выхода, при нулевом — нет. А это и соответствует передаче информационного сигнала в адресованный выходной канал.

В связи с указанным, в сериях элементов отдельные демультиплексоры могут отсутствовать, а дешифратор со входом разрешения часто называется дешифратором-демультиплексором.

Рис. 2.10. Схема наращивания мультиплексоров

Билет4

Схемы контроля четн/нечетн

Контроль правильности передач и хранения данных — важное условие нормальной работы ЦУ. В этой области простейшим и широко применяемым методом является контроль по модулю 2. Приступая к ознакомлению с этим методом, следует остановиться на некоторых понятиях из теории построения помехоустойчивых кодов. Кодовая комбинация — набор из символов принятого алфавита. Код — совокупность кодовых комбинаций, используемых для отображения информации. Кодовое расстояние между двумя кодовыми комбинациями — число разрядов, в которых эти комбинации отличаются друг от друга. Минимальное кодовое расстояние — минимальное кодовое расстояние для любой пары комбинаций, входящих в данный код. Кратностью ошибки называют число ошибок в данном слове (число неверных разрядов).

Из теории кодирования известны условия обнаружения и исправления ошибок при использовании кодов:

где dmin — минимальное кодовое расстояние кода; г обн и r и cnp — кратность обнаруживаемых и исправляемых ошибок соответственно.

Существует также понятие веса комбинации, под которым понимается число единиц в данной комбинации.

Для двоичного кода минимальное кодовое расстояние dmin=1, поэтому он не обладает возможностями какого-либо контроля производимых над ним действий. Чтобы получить возможность обнаруживать хотя бы ошибки единичной кратности, нужно увеличить минимальное кодовое расстояние на 1. Это и сделано для кода контроля по модулю 2 (контроля по четности/нечетности).

При этом способе контроля каждое слово дополняется контрольным разрядом, значение которого подбирается так, чтобы сделать четным (нечетным) вес каждой кодовой, комбинации. При одиночной ошибке в кодовой комбинации четность (нечетность) ее веса меняется, а такая комбинация не принадлежит к данному коду, что и обнаруживается схемами контроля. При двойной ошибке четность (нечетность) комбинации не нарушается — такая ошибка не обнаруживается. Легко видеть, что у кода с контрольным разрядом dmin=2. Хотя обнаруживаются ошибки не только единичной, но вообще нечетной кратности, на величину dmin это не влияет.

При контроле по четности вес кодовых комбинаций делают четным, при контроле по нечетности — нечетным. Логические возможности обоих вариантов абсолютно идентичны. В зависимости от технической реализации каналов передачи данных, может проявиться предпочтительность того или иного варианта, поскольку один из вариантов может позволить отличать обрыв всех линий связи от передачи нулевого слова, а другой — нет.

Значения контрольного разряда р при контроле по четности (р ч ) и нечетности (р н ) приведены для четырехразрядного информационного слова в табл. 2.9.

Таблица 2.9

После передачи слова или считывания его из памяти вновь производится сложение разрядов кодовой комбинации по модулю 2 (свертка по модулю 2) и проверяется, сохранилась ли четность (нечетность) веса принятой комбинации. Если четность (нечетность) веса комбинации изменилась, фиксируется ошибка операции.

Из приведенного материала следует, что контроль по модулю 2 эффективен там, где вероятность единичной ошибки много больше, чем вероятность двойной (или вообще групповой).

В частности, для полупроводниковой основной памяти компьютеров такая ситуация справедлива, т. к. каждый бит слова хранится в своей собственной ячейке, и наиболее вероятны единичные ошибки. А для памяти на магнитных носителях информации (диски, ленты) дефекты таковы, что обычно затрагивают площадь, на которой размещено несколько бит данных, поэтому для этой памяти контроль по модулю 2 неэффективен.

Билет5

Регистры — самые распространенные узлы цифровых устройств. Они оперируют с множеством связанных переменных, составляющих слово. Над словами выполняется ряд операций: прием, выдача, хранение, сдвиг в разрядной сетке, поразрядные логические операции.

Регистры состоят из разрядных схем, в которых имеются триггеры и, чаще всего, также и логические элементы.

По количеству линий передачи переменных регистры делятся на однофазные и парафазные, по системе синхронизации на однотактные, двухтактные и многотактные. Однако главным классификационным признаком является способ приема и выдачи данных. По этому признаку различают параллельные (статические) регистры, последовательные (сдвигающие) и параллельно-последовательные.

В параллельных регистрах прием и выдача слов производятся по всем разрядам одновременно. В них хранятся слова, которые могут быть подвергнуты поразрядным логическим преобразованиям.

В последовательных регистрах слова принимаются и выдаются разряд за разрядом. Их называют сдвигающими, т. К. тактирующие сигналы при вводе и выводе слов перемещают их в разрядной сетке. Сдвигающий регистр может быть нереверсивным (с однонаправленным сдвигом) или реверсивным (с возможностью сдвига в обоих направлениях).

Рис. 3.37. Схема статического регистра (а) и его условное графическое обозначение (б)

Последовательно-параллельные регистры имеют входы-выходы одновременно последовательного и параллельного типа. Имеются варианты с последовательным входом и параллельным выходом (SIPO, Serial Input — Parallel Output), параллельным входом и последовательным выходом (PISO), а также варианты с возможностью любого сочетания способов приема и выдачи слов.

В параллельных (статических) регистрах схемы разрядов не обмениваются данными между собой. Общими для разрядов обычно являются цепи тактирования, сброса/установки, разрешения выхода или приема, т. е. цепи управления. Пример схемы статического регистра, построенного на триггерах типа D с прямыми динамическими входами, имеющего входы сброса R и выходы с третьим состоянием, управляемые сигналом EZ , показан на рис. 3.37.

Для современной схемотехники характерно построение регистров именно на D-триггерах, преимущественно с динамическим управлением. Многие имеют выходы с третьим состоянием, некоторые регистры относятся к числу буферных, т. е. рассчитаны на работу с большими емкостными и/или низ-коомными активными нагрузками. Это обеспечивает их работу непосредственно на магистраль (без дополнительных схем интерфейса).

Из статических регистров составляются блоки регистровой памяти — регистровые файлы. В микросхеме типа ИР26 (серии КР1533, К555 и др.) можно. хранить 4 четырехразрядных слова с возможностью независимой и одновременной записи одного слова и чтения другого. Информационные входы регистров соединены параллельно (рис. 3.38), Входы адресов записи WA и WB (от Write) дают четыре комбинации, каждая из которых разрешает «защелкнуть» данные, присутствующие в настоящее время на выводах Di-4.

Содержимое файла (регистра) вызывается на выходы блока Q 1-4 с помощью дешифратора считывания (адресных входов мультиплексора) адресами RA и RB (от английского Read). Таких адресов четыре.

Если на входе разрешения записи WE (Write Enable) действует активный низкий уровень, то данные поступают в соответствующий регистр, при высоком уровне WE входы для данных и адресов запрещены.

Выходные данные выдаются в прямом коде.

Размерность регистровой памяти можно наращивать, составляя из нескольких ИС блок памяти. При наращивании числа хранимых слов выходы отдельных ИС с тремя состояниями соединяются в одной точке. Допускается соединять непосредственно до 128 выходов, что дает 512 хранимых слов. Ограничение на число соединяемых в одной точке выходов вызвано токовым режимом выхода, оно может быть преодолено при подключении к выходной точке специальных внешних резисторов. При наращивании разрядности слова соединяют параллельно входы разрешения и адресации нескольких ИС, выходы которых в совокупности дают единое информационное слово.

Рис. 3.38. Схема регистрового файла

Последовательные (сдвигающие) регистры представляют собою цепочку разрядных схем, связанных цепями переноса.

В однотактных регистрах со сдвигом на один разряд вправо (рис. 3.39, а) слово сдвигается при поступлении синхросигнала. Вход и выход последовательные (DSR — Data Serial Right). На рис. 3.39, б показана схема регистра со сдвигом влево (вход данных DSL — Data Serial Left), а на рис. 3.39, в иллюстрируется принцип построения реверсивного регистра, в котором имеются связи триггеров с обоими соседними разрядами, но соответствующими сигналами разрешается работа только одних из этих связей (команды «влево» и «вправо» одновременно не подаются).

Согласно требованиям синхронизации, рассмотренным в предыдущем параграфе, в сдвигающих регистрах, не имеющих логических элементов в межразрядных связях, нельзя применять одноступенчатые триггеры, управляемые уровнем, поскольку некоторые триггеры могут за время действия разрешающего уровня синхросигнала переключиться неоднократно, что недопустимо.

Триггеры с динамическим управлением или двухступенчатые могут быть использованы так, как описано в параграфе «Синхронизация в цифровых устройствах».

Появление в межразрядных связях логических элементов и, тем более, логических схем неединичной глубины упрощает выполнение условий работоспособности регистров и расширяет спектр типов триггеров, пригодных для этих схем.

Рис. 3.39. Схемы регистров сдвига вправо (а), влево (б) и реверсивного (в)

Многотактные сдвигающие регистры управляются несколькими синхро-последовательностями. Из их числа наиболее известны двухтактные с основным и дополнительным регистрами, построенными на простых одноступенчатых триггерах, управляемых уровнем. По такту С1 содержимое основного регистра переписывается в дополнительный, а по такту С2 возвращается в основной, но уже в соседние разряды, что соответствует сдвигу слова. По затратам оборудования и быстродействию этот вариант близок к одно-тактному регистру, с двухступенчатыми триггерами.

В сериях ИС и библиотеках БИС/СБИС программируемой логики имеется много вариантов регистров (в схемотехнике ТТЛШ их около 30). Среди них многорежимные (многофункциональные) или универсальные, способные выполнять набор микроопераций. Многорежимность достигается композицией в одной и той же схеме частей, необходимых для выполнения различных операций. Управляющие сигналы, задающие вид выполняемой в данное время операции, активизируют необходимые для этого части схемы.

Типичным представителем многорежимных регистров является микросхема ИР13 серии КР1533 и других (рис. 3.40). Это восьмиразрядный регистр с возможностью двусторонних сдвигов с допустимой тактовой частотой до 25 МГц при токе потребления до 40 мА. Имеет также параллельные входы и выходы, вход асинхронного сброса R и входы выбора режима So и Si, задающие четыре режима (параллельная загрузка, два сдвига и хранение). Функционирование регистра определяется табл. 3.13.

Условное обозначение регистра ИР13 приведено на рис. 3.41.

Регистры, имеющие разнотипные вход и выход, служат основными блоками преобразователей параллельных кодов в последовательные и обратно. На рис. 3.42 показана схема преобразователя параллельного кода в последовательный на основе восьмиразрядного регистра типа SI/PI/SO. В этой схеме отрицательный стартовый импульс St, задающий уровень логического нуля на верхнем входе элемента 1, создает единичный сигнал параллельного приема данных на вход L (Load — загрузка), по которому в разряды 1. 7 регистра загружается преобразуемое слово D 1-7 , а в нулевой разряд — константа 0. На последовательный вход DSR подана константа 1.

Рис. 3.40. Схема многорежимного регистра

Рис. 3.41. Условное обозначение универсального регистра

Таким образом, после загрузки в регистре формируется слово OD1D2. D7. Тактовые импульсы, поступающие на вход С, вызывают сдвиги слова вправо (для условного обозначения это соответствует сдвигу вниз). Сдвиги выводят слово в последовательной форме через выход Q7. Вслед за информационными разрядами идет ноль (константа «0»), после которого цепочка единиц. Пока ноль не выведен из регистра, на выходе элемента 2 действует единичный сигнал. После вывода нуля все входы элемента 2 становятся единичными, его выход приобретает нулевое значение и через элемент 1 формирует сигнал автоматической загрузки следующего слова, после чего цикл преобразования повторяется.

Рис. 3.42. Схема преобразователя параллельного кода в последовательный

В перечне микроопераций, выполняемых регистрами, были указаны поразрядные логические операции. Современные регистры мало приспособлены для выполнения этих операций, однако при необходимости их можно выполнить, пользуясь регистрами на RS-триггерах. Для выполнения операции ИЛИ на S-входы статического регистра с исходным нулевым состоянием подается первое слово А, единичные разряды которого устанавливают соответствующие триггеры. Затем без сброса регистра на S-выходы подается второе слово В. Ясно, что в результате получим результат Q = А\/В.

При выполнении поразрядной операции И в первом такте на S-входы регистра подается слово А, устанавливающее те разряды регистра, в которых слово А имеет единицы. Затем следует подать на регистр слово В. Чтобы в регистре сохранились единицы только в тех разрядах, в которых единицы имеют оба слова, слово В подается на входы R триггеров в инверсном виде.

Сложение по модулю 2 может быть выполнено схемой с триггерами типа Т в разрядах путем последовательной во времени подачи на нее двух слов А и В.

Источник