Сравнение основных параметров БЛЭ

Лекция №3

Базовые логические элементы

1. Способы представления логических переменных электрическими сигналами

2. Логические элементы на базе биполярных транзисторных структур

3. Логические элементы на базе МОП транзисторов

4. Основные параметры БЛЭ

5.Сравнение основных параметров БЛЭ

Способы представления логических переменных электрическими сигналами

1.1 Потенциальный способ кодирования »0» и »1».

Понятие о положительной и отрицательной логиках.

1.4. Импульсный способ кодирования »0» и »1» (в виде импульсов, перепадов напряжения). Параллельный и последовательный способы передачи данных

Логические элементы на базе биполярных транзисторных структур

Логический элемент 4И-НЕ типа ТТЛ

|

Рисунок 2 – Логический элемент 4И-НЕ типа ТТЛ

Логический элемент 4И-НЕ типа ТТЛШ

Рисунок 3 – Логический элемент 4И-НЕ типа ТТЛШ

| Тип | ТТЛ | ТТЛ | ТТЛШ | ТТЛШ | ТТЛШ |

| Серия | К155 | К134 | К1530 | К555 | К1533 |

| P ср потр,мВт | ≤20,0 | ≤2,0 | ≤35 | ≤4 | ≤4 |

| τзд,нс | ≤19,0 | ≤80,0 | ≤5,0 | ≤20,0 | ≤20 |

Эмиттерно-связанная логика (ЭСЛ элементы)

| Вх2 | Вх1 | Вых1/ ИЛИ-НЕ | Вых2/ ИЛИ |

| 1 (-0,9) | 0 (-1,7) |

Pпотр = 25 – 30 мВт, τзд= 0,5 – 3 нс (серия 1500).

Рисунок 4 – Логический элемент типа ЭСЛ с выходами ИЛИ-НЕ/ ИЛИ

4.4 Интегрально-инжекционная логика (И 2 Л)

4.4.1 Принцип действия И 2 Л

| U1 | U2 | Iб3 | Iб4 | Iвых | Uвых |

Рисунок 5 – Логический элемент ИЛИ-НЕ типа И 2 Л

4.4.2 Элемент ИЛИ-НЕ /ИЛИ на основе И 2 Л

| Вх1 | Вх0 | Вых1 | Вых2 |

Рисунок 6 – Логический элемент ИЛИ-НЕ/ИЛИ типа И 2 Л

Особенности выходных каскадов

Схема с открытым коллектором

Рисунок 8 – Схема с открытым коллектором

Схема с тремя состояниями ( Z — состоянием)

Рисунок 9 – Схема с тремя состояниями

Логические элементы на базе МОП — транзисторов

Рисунок 2 – Логические элементы ИЛИ-НЕ (а) и И-НЕ (б) на МОП-транзисторах n-типа

Pпотр = 0,1 – 1,5 мВт, τзд= 1 – 100 нс

Рисунок 3 – Логические элементы И-НЕ (а) и ИЛИ-НЕ (б) на КМОП-транзисторах

P стат потр = 100 мВт, P динам потр = 1 — 5 мВт, τзд= 10 – 100 нс

Основные параметры и свойства БЛЭ

Совместимость входных и выходных уровней сигналов

Для надежной работы и выполнения заданных логических функций диапазон уровней выходных сигналов БЛЭ для лог.1 и лог.0 (заштрихованная область) должен находиться в диапазоне уровней входных сигналов БЛЭ для лог.1 и лог.0 в случае температурных изменений или технологических разбросов уровней в процессе производства.

4.2 Нагрузочная способность:

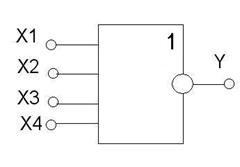

· Коэффициент объединения по входу Коб = 2 – 8;

· Коэффициент разветвления по выходу Кразв = 4 – 10.

Для мощных цифровых усилителей Кразв = 20 – 30.

Передаточная характеристика.

.

Формирующее свойство (свойство квантования сигнала).

Статическая помехоустойчивость.

Динамическая помехоустойчивость

Временные параметры

4.7 Потребляемая мощность Рпотр.

4.8 энергия переключения Эпркл = tср. ×Рпотр

4.9 Технологический разброс электрических и конструкционных параметров.

4.10 Условия эксплуатации, характеризуемые последовательностью дестабилизирующих факторов: диапазон рабочих температур, допустимое изменение напряжений питания, допустимые механические воздействия.

Сравнение основных параметров БЛЭ

5.1 Элементы типа ТТЛ, ЭСЛ, И 2 Л, n-МОП и p-МОП, К-МОП: преимущества и недостатки.

Источник

4. Способы физического представления логических переменных.

Для этой цели в электронных логических схемах используются электрические сигналы. Различают потенциальный и импульсный способы представления логических переменных.

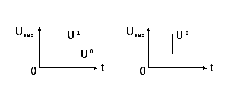

При потенциальном способе двум значениям переменной а (0 и 1) ставятся в соответствие два значения потенциала:

которые могут быть как положительными, так и отрицательными(рис. 3)

Логика называется положительной (в дальнейшем мы будем рассматривать только такую логику), если высокий и низкий потенциалы отображают соответственно

При импульсном способе представления двум значениям (1 и 0) ставиться в соответствие появление или непоявление импульса e (рис. 4) в определённые моменты, фиксируемые тактовыми импульсами.

Тактовые импульсы вырабатываются стабилизированным по частоте генератором с частотой

5. Синтез комбинационных цепей.

Цифровым узлом комбинационного типа называют логическое устройство, выходные сигналы которого зависят только от сигналов, поданных на его входы в данный момент времени. В комбинационных схемах (КС) элементы памяти отсутствуют, так что сигналы, действующие на входы (КС), не сохраняются. Поэтому КС применяются для ограниченного числа операций и используются в основном в качестве шифраторов, дешифраторов, преобразователей кода и схем контроля.

Синтез КС включает следующие этапы:

Составление таблицы Функционирования.

Запись логической функции и её минимизация.

Составление функциональной схемы по минимизированному выражению.

Разработка принципиальной схемы с учётом выбранной серии интегральных схем.

Рассмотрим несколько простейших КС.

Пороговая ячейка находит применение в устройствах автоматического контроля состояния нескольких объектов. Сигнал на выходе трехвходовой, например, ячейки будет равен 1 только тогда, когда на её входах (а, в, с) присутствует не менее двух единичных сигналов.

Таблица функционирования (табл.1) имеет три столбца, содержащих восемь различных комбинаций входных сигналов, причем четырем из них соответствует выходной сигнал, равный 1.

Пользуясь таблицей, можно записать логическую функцию, которую должна выполнять синтезирующая цепь. Для этого функция представляется в виде суммы простых конъюнкций, соответствующих тем сторонам таблиц, для которых

Упрощая эту функцию известными способами, которые здесь не рассматриваются (смотри, например, /1/), получим:

Если воспользоваться для построения логической цепи элементами “И-НЕ”, имеет смысл преобразовать функцию следующем образом:

Из последнего видно, что для построения пороговой ячейки требуется 3 двухвходовых и 1 трёхвходовый элемент ”И-НЕ” (рис. 5).

Сумматор — это такая логическая цепь, которая вырабатывает сигналы суммы (Si) и переноса (Pi) при поступлении на ее входы сигналов слагаемых (ai и bi) и сигналов переноса с предыдущего разряда (Рi-1). Сумматор является одним из основных узлов цифровых вычислительных машин.

Н

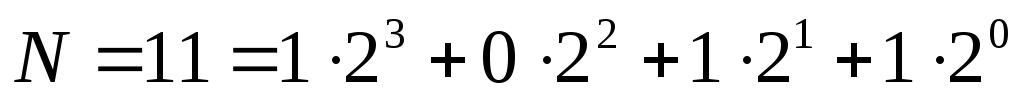

где коэффициенты аi, (двоичные цифры) принимают одно из двух значений 0 или 1. Отдельные слагаемые в сумме называются разрядами числа, старшинство разрядов определяется множителем 2 i . При написании числа в двоичной системе применяется сокращенная форма, когда в определённом порядке записываются только двоичные цифры, причем справа располагаются цифры более младших разрядов. Так, например, число

в двоичной системе будет иметь вид N= 1011

Сложение, как, впрочем, и остальные арифметические действия, в двоичной системе выполняются точно также как аналогичные операции с десятичными числами. В качестве примера рассмотрим сложение чисел 11(1011) и 9(1001). В скобках дана запись чисел 11 и 9 в двоичной системе.

Источник

9.5. Представление логических переменных электрическими сигналами

В настоящее время в цифровой технике широко применяется потенциальный способ представления логических переменных и логических функций. Потенциальный способ представления ставит в соответствие логическим 1 и 0 два различных уровня напряжения (см. рис. 9.3). Представление логической 1 высоким уровнем – U 1 , а логического 0 – низким – U 0 называют положительной логикой (рис. 9.3а). Представление логического 0 высоким уровнем – U 0 , а логической 1 – низким – U 1 называют отрицательной логикой (рис. 9.3б). В дальнейшем будем рассматривать цифровые устройства, работающие на потенциальной положительной логике.

Рис. 9.3. Потенциальный способ представления логических переменных и

9.6. Базовые логические элементы. Их классификация,

схемотехника и принцип действия

Особенности построения ЛЭ. В настоящее время по технологическим и потребительским свойствам находит широкое применение элементная база цифровых устройств на биполярных и полевых транзисторах. Транзисторы работают в режиме ключа (открыт, закрыт). При работе в ключевом режиме транзисторы не чувствительны к разбросу параметров, поэтому для схем не нужна настройка, что позволяет автоматизировать изготовление ЛЭ. Во многих схемотехнических решениях ЛЭ ток протекает только в момент переключения из одного в другое состояние, поэтому ЛЭ рассеивают малую мощность, что позволяет располагать много транзисторов в малом объеме, т.е. реализовать миниатюрные ЛЭ. Цифровые электронные схемы выпускаются в виде интегральных схем (ИС). Сложность ИС характеризуется степенью функциональной интеграции:

На биполярных транзисторах реализуют ИС следующих типов логики: транзисторно-транзисторная логика (ТТЛ), эмиттерно-связная логика (ЭСЛ), интегральная инжекционная логика (И 2 Л). Наряду с ними широко применяются ИС на полевых транзисторах с изолированным затвором, т.н. МОП-структуры (МОП логика), а также на комплементарных полевых транзисторах с каналами р- и n-типа, т.н. КМОП логика (КМОПЛ). На практике широко применяются ИС ТТЛ серии К155 и ИС КМОПЛ серий К176, К561. ИС КМОП логики технологичны в изготовлении, обладают повышенной степенью интеграции.

На рис. 9.4 показана схема базового ЛЭ ТТЛ. Многоэмиттерный транзистор VT1, включенный на входе и который может иметь от двух до восьми входов (эмиттеров), выполняет логическую функцию И. Транзисторы VT2, VT3, VT4 образуют сложный инвертор, выполняющий логическую функцию НЕ. На транзисторе VT2 и резисторах R2, R3 собран предварительный фазоинвертирующий усилитель. На транзисторах VT3 и VT4 собран выходной усилитель. Все транзисторы работают в ключевом режиме. При хотя бы одном нулевом входном сигнале транзистор VT1 открыт и находится в режиме насыщения. Напряжение коллектора VT1 в этом случае низкое. Поскольку UБ2 = UК1, то транзистор VT2 закрыт и UК2 = EП, а UЭ2 = 0. Так как UБ3 = UК2, а UБ4 = UЭ2, то транзистор VT3 открыт, а транзистор VT4 – закрыт и UВЫХ = UК4 = EП, что соответствует высокому уровню Y = 1. Если на всех входах высокое напряжение (логическая 1), то транзистор VT1 оказывается включенным инверсно (коллектор и эмиттер меняются ролями) и малый ток, протекающий через R1 и коллекторный переход VT1, создает на них малое падение напряжения. Это в свою очередь обеспечивает напряжение на базе VT2 (UБ2 > 0,8 В) достаточное для перевода транзистора в режим насыщения. Ток, протекающий в цепи R2, VT2, R3, создает низкое напряжение UБ3 = UК2 (транзистор VT3 закрыт) и высокое напряжение UБ4 = UЭ2 (транзистор VT4 насыщен). В режиме насыщения UВЫХ = UК4 составляет порядка 0,4 В, что соответствует низкому уровню Y = 0. Следовательно, рассмотренная схема выполняет функцию И-НЕ. Диод VD4 обеспечивает дополнительное смещение напряжения на эмиттере VT3 для его надежного запирания. Диоды VD1-VD3 – демпферные, защищают входы при переходных процессах в моменты переключений. Включение диодов VD1 — VD4 является типовым приемом интегральной технологии для защиты схем от ложного срабатывания.

Показанная на рис. 9.5а комплементарная пара полевых транзисторов с индуцированными каналами (один p-типа, другой n-типа) образует идеальный переключатель напряжения. Когда на входе действует напряжение высокого уровня, p-канальный транзистор закрыт, а n-канальный открыт. В случае напряжения низкого уровня на входе – транзистор n-типа закрыт, а p-типа открыт, т.е. комплементарная пара выполняет функцию НЕ. Отсутствие сквозного тока обеспечивает малую потребляемую мощность, что является важным достоинством КМОП-логики.

Рис. 9.4. Схема базового ЛЭ ТТЛ

Рис. 9.5. Схема базовых ЛЭ КМОПЛ

Базовые ЛЭ КМОПЛ И-НЕ и ИЛИ-НЕ показаны на рис. 9.5б, 9.5в. ЛЭ И-НЕ образуется последовательным соединением n-канальных транзисторов и параллельным – р-канальных. Если хотя бы на одном входе действует логический 0, то последовательная цепь n-канальных транзисторов разомкнута и на выходе Y = 1. В этом случае, если схема нагружена, то через открытые p-канальные транзисторы и нагрузку будет протекать ток от источника питания. Только при подаче на все входы логической 1 открытые n-канальные транзисторы замкнут выход на корпус, и получим Y =0. Кроме этого закрытые p-канальные транзисторы отключают нагрузку от источника питания. Нетрудно убедиться, что схема с параллельным соединением n-канальных транзисторов и последовательным p-канальных выполняет функцию ИЛИ-НЕ.

ЛЭ характеризуются рядом статических и динамических параметров. К ним относятся напряжение источника питания, уровни напряжений логических 0 и 1, нагрузочная способность, помехоустойчивость, быстродействие, потребляемая мощность. Статические свойства схемы наглядно отражаются ее передаточной характеристикой – зависимостью напряжения на выходе от напряжения на одном из входов (рис. 9.6). Для схемы И-НЕ передаточную характеристику снимают при подаче одинаковых сигналов на входы. В этом случае она выполняет функцию инвертора. Изменяя UВХ, измеряют и строят зависимость UВЫХ=f(UВХ). По точкам, где коэффициент усиления K=UВЫХ/UВХ=1, определяют минимальное значение уровня логической 1 –

Рис. 9.6. Передаточная характеристика ЛЭ НЕ

Источник